# A New Method to Fin-width Line Edge Roughness Effect of FinFET

### **Performance**

Yu Zhu<sup>1</sup>, Wei Zhao<sup>1</sup>, Wenping Wang<sup>1</sup>, Wen Wu<sup>1</sup>, Zhuqing Feng<sup>2</sup>, Caixia Du<sup>1</sup>, Jin He<sup>1\*</sup>, Ping He<sup>3</sup>, and Lei Song<sup>4</sup>

<sup>1</sup>Peking University Shenzhen SOC Key Laboratory, PKU-HKUST Shenzhen-Honkong Institutios, Shenzhen, P. R. China

<sup>2</sup>Shenzhen Huayue terascale chip Co., Ltd, Shenzhen, P. R. China

<sup>3</sup> Shenzhen Emperor Electronic Technology Co., Ltd, Nanshan District, Shenzhen,518108, China

<sup>4</sup> Shenzhen SuperD Co. Ltd, Huaqiaocheng, Nanshan District, Shenzhen 518053, China

#### **Abstract**

This paper developed a full three-dimensional (3-D) statistical simulation method to investigate Fin-width Line Edge Roughness (LER) effect on the FinFETs performance. The line edge roughness is introduced by Matlab program, and then the intrinsic parameter fluctuations at fixed LER parameters are studied in carefully designed simulation experiments. The result shows that Fin-width LER causes a dramatic shift and fluctuations in threshold voltage. The simulation results also imply that the velocity saturation effect may come into effect even under low drain voltage due to LER effect.

Keywords: Fin-width, LER, intrinsic parameter fluctuation, FinFET, 3-D numerical simulation.

### 1 Introduction

In recent years, the mainstream of the CMOS integrated circuits is arriving at 32 nanometer size and beyond. According to the SIA national technology roadmap, devices built at this scale are required to control gate length within approximately 8 nm [1]. However, with the process of lithography and etching, random deviation of the line edge from its ideal pattern, which is called line edge roughness (LER), does not scale with the critical dimension. As a result, intrinsic parameters fluctuations in deep nanometer dimensions caused by LER deserve adequately attentions.

Numerous simulations and experiments on the impact of line edge roughness [2-4] have been reported.

FinFET [5] exhibit its strong control of lightly doped channels and good immunity of short channel effect [6]. However, as mentioned above, LER plays a significant role on the transistor operation of nanoscale FinFETs.

A Fourier synthesis technique base on the power spectrum of a Gaussian autocorrelation function was used for LER analysis in planar bulk MOSFETs, and the geometrical variation effects was also systemically studied [4].

In this paper, the LER issue in FinFETs is investigated through a full 3-D statistical simulation approach. The Fin-width roughness is first generated using Matlab program. Then, the variation of on-current Ion, off-current Ioff, voltage threshold VT, transconductance (gm) and subthreshold slope SS are studied in a series of simulation experiments. Finally we analyze the performances of synchronic technological parameter devices under different work conditions.

## 2 Simulation approach

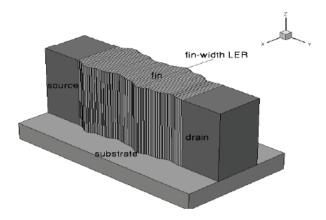

In this paper, TCAD 3-D numerical simulator is applied for FinFET performance simulation. The structure of double-gate n-channel FinFETs studied here is shown in Fig. 1. The Fin-width roughness modeling approach is based on a sequence of fixed root-mean-square amplitude by Matlab. The parameters used to generate the edges are

root-mean-square amplitude  $\Delta$  and a cut-off frequency  $f_H$ , which reflects the nature of LER in the simulation. Experimentally,  $\Delta$  is relative to the standard deviation of Fin-width and  $f_H$  is determined by suiting a particular Fourier transformation of the fin edges.

Figure 1: Three-dimension schematic of simulated DG FinFETs with Fin-width LER (Omit the gate).

In the process of Fin-width generation, a premier sequence S is first produced as follow:

$S = average-value-of-Fin-width + \Delta \times randn(1,N)$

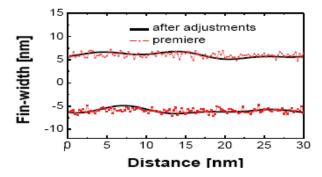

The Fourier transformation of S is consequently obtained. Then, a frequency, which is higher than cut-off frequency fH as zero in S, is set to fit a specific fin edges for real. After obtaining a new sequence S1 by Fourier transformation, a series of adjustments are applied to equal the average value as well as the standard deviation of S1 to those of the premiere S. To be specific, Fig. 2 set an example of a particular resist-defined fin following that method.

Nominal geometry and correlation parameters are listed in Table 1. To compare with the practical parameters, data used in this work is referred to [4] and [6]. Linearity threshold voltage  $V_{T,lin}$  and saturation threshold voltage  $V_{T}$ , sat have been calculated through a constant current method at  $V_{ds} = 50 \text{mV}$  and  $V_{ds} = 1 \text{V}$ , respectively. In addition,  $I_{on}$  and  $I_{off}$  have been extracted in the saturation regime ( $V_{ds} = 1 \text{V}$ ) at  $V_{gs} = 1 \text{V}$  and  $V_{gs} = 0 \text{V}$ , respectively. Subthreshold slope is detected based on device characteristic curve. With respect to the dramatic quantum effects due to the small dimension, we apply the density gradient method. As for

most analog applications operate in saturation regime, high drain bias conditions is focused for the mismatch estimation.

Figure 2: Example of resist defined fin generation. The LER parameters used to define the fin edges are  $\Delta = 0.71$ nm and fH=6.

Table 1: Simulated double-gate FinFETs' parameters.

| Parameter       | Value | Parameter  | Value                   |

|-----------------|-------|------------|-------------------------|

| $ m W_{fin}$    | 12nm  | length of  | 10nm                    |

| ${ m H_{fin}}$  | 20nm  | channel    | p-type 10 <sup>17</sup> |

| Lgate           | 30nm  | S/D doping | n-type 10 <sup>20</sup> |

| t <sub>ox</sub> | 1.5nm |            |                         |

#### 3 Simulation results

We assume the root-mean-square amplitude  $\Delta$  of Fin-width LER 0.71nm, which means variation fluctuations to be 10% of its critical dimension.

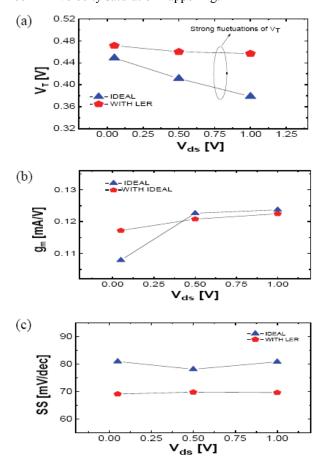

Fig. 3 compares the average value of  $V_{T,lin}$ ,  $V_{T,sat}$ ,  $SS,g_m$  due to Fin-width LER to the ideal values without LER effects. As shown in Fig. 3 (a), the threshold voltage increases with Fin-width LER due to enhanced short channel effect. Meanwhile, the increase of drain voltage results in severe threshold voltage fluctuations, which is comparable to those resulting from similar 30nm FinFETs in [6]. Observed from Fig. 3 (c), SS almost remains constant with the increased drain voltage. Moreover, SS turns out to be smaller with Fin-width LER, which indicates a better device performance in subthreshold region. This result is owing to the dramatic decrease of  $I_{off}$  when considering only Fin-width roughness.

Table 2: Average value of Ion and Ioff on different drain voltages.

| Average | $V_{ds}=50mV$ | $V_{ds}=1.0V$ |

|---------|---------------|---------------|

|---------|---------------|---------------|

| I <sub>on</sub> (A/um)  | 3.029×10 <sup>-5</sup>  | 3.117×10 <sup>-5</sup>  |

|-------------------------|-------------------------|-------------------------|

| I <sub>off</sub> (A/um) | 2.147×10 <sup>-14</sup> | 3.491×10 <sup>-14</sup> |

From Table 2, it can be seen that drive current  $I_{on}$  as well as leakage current  $I_{off}$  of  $V_{ds} = 1V$  and  $V_{ds} = 50 \text{mV}$  remain surprisingly close to each other. Combining the close result of  $V_{ds} = 1V$  and  $V_{ds} = 50 \text{mV}$  in Fig. 3, it seems those two conditions similar to each other. This is because of the velocity saturation effect in the channel. Since the fin is ultra thin, the electric-field intensity is extraordinarily high. Considering this electric-field intensity to be  $10^5 \text{V/cm}$ , we confirm velocity saturation happening.

Figure 3: Comparison of ideal FinFETs' performance with those of Fin-width LER on average value of (a) VT,sat, (b) gm, (c) SS. The LER parameters used to define the fin edges are  $\Delta$  = 0.71nm and fH=6.

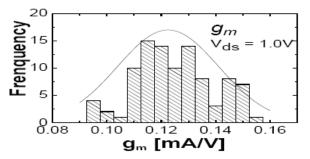

Figure 4: Distributions of the  $g_m$  under high drain voltage with  $\Delta = 0.71$ nm and  $f_H=6$ .

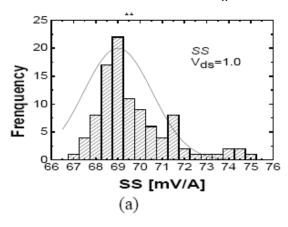

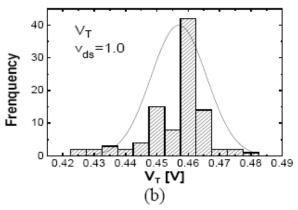

Figure 5: Distributions of the (a) SS and (b)  $V_T$  under high drain voltage with  $\Delta = 0.71$ nm and  $f_H=6$ .

Fig. 4 and Fig. 5 shows typical distributions of transconductance, threshold voltage and subthreshold slope in 30 nm FinFETs corresponding to Fin-width LER under high drain voltage ( $V_{ds}=1V$ ). These are almost close to a Gaussian distribution. Combining the fact that threshold voltage does show a dramatic shift compared with an ideal on, which is illustrated in Fig. 3(a), it infers that the threshold voltage in saturation region is largely affected by LER. Typical distributions of threshold voltage and

subthreshold slope at low drain voltage ( $V_{ds} = 50 mV$ ) are illustrated in Fig. 6, subthreshold slope and the threshold voltage distribution in subthreshold region shows highly concentration. This difference is owing to two facts. One is that Fin-width LER mainly influences the channel direction. The other is the extreme low voltage of  $V_{ds}$ , which is along the channel direction. With respect to those two facts, the device characteristic in subthreshold region is affected relatively to a small extent by Fin-width LER.

Figure 6: Distributions of the (a) SS and (b) VT under low drain voltage with  $\Delta = 0.71$ nm and fH=6.

### 4 Conclusion

The LER effect is investigated using Matlab in this paper for the first time. The Fin-width LER is demonstrated to be a critical source of intrinsic parameter fluctuations in nanometer FinFETs, especially for the threshold voltage. Velocity saturation effect has been proved to occur even under low drain voltage. As under high drain voltage, the distributions of VT, SS and gm match a Gaussian distribution, which indicating the influence of Fin-width LER along the channel direction.

### Acknowledgment

This work is funded by National Natural Science Foundation of China under Grants (61574005, 61306042, 61306045, 61306132, and 61274096). This work is also supported by the Fundamental Research Project of Shenzhen Science & Technology Foundation JCYJ 20140721163526514, and the International Collaboration Project of Shenzhen Science & Technology Foundation (GJHZ2015031615060422, SGLH20150213140604619).

### References

- Semiconductor Industry Association, The National Technology Roadmap for Semiconductors, 1999 Edition, pp. 89.

- S. Xiong, and 1. Bokor, "A simulation study of gate line edge roughness effects on doping profiles of short-channel MOSFET devices," Vol. 51, No.2,IEEE Trans. Electron Devices, Feb. 2004, pp. 228-232.

- T. Linton, M. Chandhok, B. 1. Rice, and G. Schrom, "Determination of the line edge roughness specification for 34nm devices," in IEDM Tech. Dig., 2002, pp. 303-306.

- Shimeng Yu, Yuning Zhao, Yuncheng Song, Gang Du, Jinfeng Kang, Ruqi Han, and Xiaoyan Liu, "3-D simulation of geometrical variations impact on nanoscale FinFETs," Solid-State and Integrated-Circuit Technology, 2008. ICSICT 2008. 9th International Conference on 20-23 Oct. 2008, pp. 408 – 411.

- D. H. W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano,

C. Kuo, E. Anderson, T.-J. King, J. Bokor, and C. Hu,

"FinFET—a self-aligned double-gate MOSFET scalable to 20 nm," Vol. 47, No. 12, IEEE Trans.

Electron Devices, Dec. 2000, pp. 2320–2325.

- Emanuele Baravelli, Malgorzata Jurczak, Nicol'o Speciale, Kristin De Meyer, and Abhisek Dixit, "Impact of LER and Random Dopant Fluctuations on FinFET Matching Performance, " Vol. 7, No. 3, IEEE Transactions on nanotechnology, MAY 2008, pp. 291 – 298.