# Simulation of Lags and Current Collapse in Field-Plate AlGaN/GaN HEMTs with Different Types of Buffer Layers

R. Tsurumaki, N. Noda and K. Horio

Faculty of Systems Engineering, Shibaura Institute of Technology 307 Fukasaku, Minuma-ku, Saitama 337-8570, Japan, horio@sic.shibaura-it.ac.jp

#### ABSTRACT

We make 2-D transient simulations of field-plate AlGaN/GaN HEMTs with a semi-insulating buffer layer, where a deep acceptor above the midgap is considered. It is studied how the deep acceptor and the field plate affect lag phenomena and current collapse. It is shown that the drain lag and current collapse could be reduced by introducing a field plate, as in a case with a deep acceptor compensated by a deep donor in the buffer layer. This reduction occurs because electron trapping by the deep acceptors is weakened by the field plate. The dependence on the fieldplate length and the insulator thickness under the field plate is also studied, showing that the rates of lags and current collapse are quantitatively similar between the two cases with different types of buffer layers when the deep-acceptor density in the buffer layer is the same.

*Keywords*: GaN, HEMT, deep acceptor, current collapse, field plate

#### **1 INTRODUCTION**

In AlGaN/GaN HEMTs, slow current transients are often observed even if the gate voltage or the drain voltage is changed abruptly [1]. This is called gate lag or drain lag, and is problematic for circuit applications. The slow transients mean that dc I-V curves and RF I-V curves become quite different, resulting in lower RF power available than that expected from the dc operation [2]. This is called current collapse. These are serious problems, and many experimental works are reported [1-5], and several theoretical works are made [5-10]. In previous theoretical works, the semi-insulating buffer is treated as undoped, and a deep donor and a deep acceptor are considered in it [6, 7], and the effects of a field plate on buffer-related lags and current collapse are also studied [9, 10]. Recently, a Fedoped semi-insulating buffer layer is often adopted, and Fe acts as a deep acceptor [11]. Therefore, in this work, we have made simulations of field-plate AlGaN/GaN HEMTs with a buffer layer including only deep acceptors, and found that the buffer-related lags and current collapse are quite similar between the two cases.

#### 2 PHYSICAL MODEL

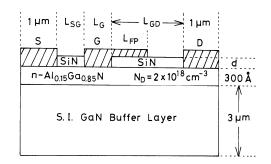

Figure 1 shows a modeled device structure analyzed in

Figure 1: Device structures simulated in this study.

this study. The gate length  $L_{\rm G}$  and the field-plate length  $L_{\rm FP}$  are typically set to 0.3 µm and 1µm, respectively. As a buffer layer, we consider a Fe-doped semi-insulating buffer layer. The Fe-level ( $E_{\rm DA}$ ) is set to 0.5 eV below the bottom of conduction band, and it is assumed to act as a deep acceptor. Here the deep acceptor acts as an electron trap. The deep-acceptor density  $N_{\rm DA}$  is set to 10<sup>17</sup> cm<sup>-3</sup> here.

Basic equations to be solved are Poisson's equation including ionized deep-acceptor terms, continuity equations for electrons and holes which include carrier loss rates via the deep acceptor and rate equations for the deep acceptor [7, 12-16].

1) Poisson's equation

$$\nabla \bullet (\varepsilon \nabla \psi) = -q(p - n + N_{\rm D} - N_{\rm DA}^{-}) \tag{1}$$

2) Continuity equations for electrons and holes

$$\frac{\partial n}{\partial t} = \frac{1}{q} \nabla \bullet J_n - R_{n,\text{DA}}$$

(2)

$$\frac{\partial p}{\partial t} = -\frac{1}{q} \nabla \bullet J_p - R_{p,\text{DA}}$$

(3)

where

$$R_{n,\text{DA}} = C_{n,\text{DA}} (N_{\text{DA}} - N_{\text{DA}}^{-}) n - e_{n,\text{DA}} N_{\text{DA}}^{-}$$

(4)

$$R_{p,\text{DA}} = C_{p,\text{DA}} N_{\text{DA}}^{-} p - e_{p,\text{DA}} (N_{\text{DA}} - N_{\text{DA}}^{-})$$

(5)

3) Rate equation for the deep acceptor

$$\frac{\partial}{\partial t}N_{\rm DA}^{-} = R_{n,\rm DA} - R_{p,\rm DA} \tag{6}$$

where  $N_{\text{DA}}^{-}$  represents the ionized deep-acceptor density.  $C_{n,\text{DA}}$  and  $C_{p,\text{DA}}$  are the electron and hole capture coefficients of the deep acceptor, respectively,  $e_{n,\text{DA}}$  and  $e_{p,\text{DA}}$  are the electron and hole emission rates of the deep acceptor, respectively. These are given as functions of the

PAST TIME[sec]

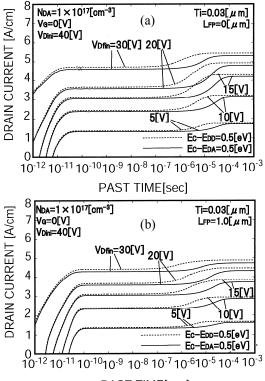

Figure 2: Calculated drain-current responses of AlGaN/GaN HEMTs when  $V_{\rm D}$  is changed abruptly from 40 V to  $V_{\rm Dfin}$ , while  $V_{\rm G}$  is kept constant at 0 V. d = 0.03 µm.  $N_{\rm DA} = 10^{17}$  cm<sup>-3</sup>. (a) Without field plate, (b) with field plate ( $L_{\rm FP} = 1$ µm).

deep acceptor's energy level and the capture cross sections.

These basic equations are put into discrete forms and are solved numerically. We have calculated the draincurrent responses when the drain voltage  $V_{\rm D}$  and/or the gate voltage  $V_{\rm G}$  are changed abruptly.

### **3 DRAIN LAG**

Figure 2 shows calculated drain-current responses of AlGaN/GaN HEMTs when  $V_{\rm D}$  is lowered abruptly from 40 V to  $V_{\text{Dfin}}$ , where  $V_{\text{G}}$  is kept constant at 0 V. The dashed lines show the case with an undoped buffer layer with  $N_{\rm DA}$ =  $10^{17}$  cm<sup>-3</sup> and  $E_{\rm C}$  -  $E_{\rm DD}$  = 0.5 eV, where  $E_{\rm DD}$  is the deep donor's energy level. Figure 2(a) shows the case without a field plate ( $L_{\rm FP} = 0$ ) and Fig.2(b) shows the case with a field plate ( $L_{\rm FP} = 1 \ \mu m$ ). Here the thickness of SiN passivation layer d is 0.03  $\mu$ m. In both cases, the drain currents remain at low values for some periods and begin to increase slowly, showing drain-lag behavior. It is understood that the drain currents begin to increase when the deep acceptors in the buffer layer begin to emit electrons, because the state of higher  $V_{\rm D}$  is a state where more electrons are captured by the deep acceptors. It is seen that the change of drain current is smaller for the case with a field plate, indicating that the drain lag is smaller for the field-plate structure.

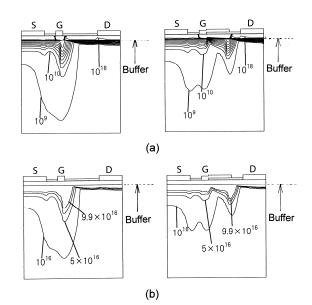

Figure 3: (a) Electron density profiles and (b) ionized deepacceptor density  $N_{\text{DA}}^{-}$  profiles at  $V_{\text{G}} = 0$  V and  $V_{\text{D}} = 40$  V.  $d = 0.03 \ \mu\text{m}$ .  $N_{\text{DA}} = 10^{17} \text{ cm}^{-3}$  and  $E_{\text{C}} - E_{\text{DA}} = 0.5$  eV. The left is for the case without a field plate, and the right is for the field-plate structure ( $L_{\text{FP}} = 1 \ \mu\text{m}$ ).

Comparing the solid and dashed lines, the response is a little faster for the case with the undoped buffer (and the current change is almost the same), but the reason of the faster response is not clear now. We will discuss below why the reduction in drain lag due to the field plate arises.

Figure 3 shows (a) electron density profiles and (b) ionized deep-acceptor density  $N_{DA}^{-}$  profiles at  $V_{G} = 0$  V and  $V_{\rm D}$  = 40 V. The left shows the case without a field plate, and the right shows the case of field-plate structure. In Fig.3(a), it is seen that without a field plate, electrons are injected deeper into the buffer layer under the gate, particularly under the drain edge of the gate region. These electrons are captured by the deep acceptors, and hence  $N_{\rm DA}^{-}$  increases there as seen in Fig.3(b). As mentioned before, when  $V_{\rm D}$  is lowered abruptly, the drain current remains at a low value for some periods and begins to increase slowly as the deep acceptors begin to emit electrons (and  $N_{DA}^{-}$  decreases), showing drain lag. In the case of field-plate structure, as seen in Fig.3(a), electrons are injected into the buffer layer under the drain edge of field plate as well as under the gate. But the injection depth is not so deep as compared to the case without a field plate. This is because the electric field at the drain edge of the gate becomes weaker by introducing a field plate. Hence, the change of  $N_{\rm DA}$  by capturing electrons is smaller for the field-plate structure as seen in Fig.3(b). Therefore, the drain lag becomes smaller for the structure with a field plate.

## 4 CURRENT COLLAPSE

Next, we have calculated a case when  $V_G$  is also changed from an off point.  $V_G$  is changed from threshold

voltage  $V_{\text{th}}$  to 0 V, and  $V_{\text{D}}$  is changed from 40 V to  $V_{\text{Don}}$  (on-state drain voltage). The characteristics become similar to those in Fig.2, although some transients arise when only  $V_{\text{G}}$  is changed (gate lag). From these turn-on characteristics, we obtain a quasi-pulsed *I-V* curve.

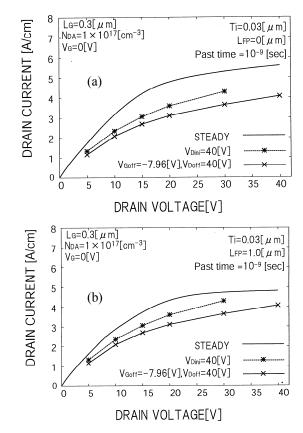

In Fig.4, we plot by ( $\Box$ ) the drain current at  $t = 10^{-9}$  s after  $V_{\rm G}$  is switched on. Figure 4(a) shows the case without a field plate, and Fig.4(b) shows the case of field-plate structure ( $L_{\rm FP} = 1 \mu m$ ). These curves are regarded as quasipulsed *I-V* curves with pulse width of  $10^{-9}$  s. They stay rather lower than the steady-state *I-V* curves (solid lines), indicating gate lag and current collapse behavior. Note that the gate lag is rather large [17]. In Fig.4, we also plot another pulsed *I-V* curve ( $\circ$ ), which is obtained from Fig.2 (where only  $V_{\rm D}$  is changed), indicating drain-lag behavior. From Fig.4, we can definitely say that the lag phenomena (drain lag, gate lag) and current collapse become smaller for the structure with a field plate.

## 5 FIELD-PLATE PARAMETER DEPENDENCE

We have next studied dependence of lag phenomena and current collapse on the field-plate length  $L_{\text{FP}}$  and the SiN thickness *d*.

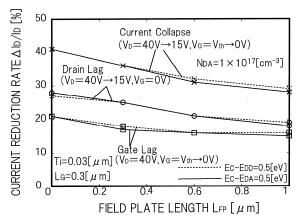

Figure 5 shows drain-current reduction rate  $\Delta I_D/I_D$ ( $\Delta I_D$ : current reduction,  $I_D$ : steady-state current) due to current collapse, drain lag or gate lag as a function of  $L_{\rm FP}$ . As  $L_{\rm FP}$  becomes longer, the current collapse and the lag phenomena becomes weaker. This is because the electric field at the drain edge of the gate is more reduced and the electron injection into the buffer layer becomes weaker. It is also seen that the characteristics are quite similar between the two cases with different types of buffer layers. Note that the acceptor density is the same for the two cases ( $N_{\rm DA} = 10^{17} \, {\rm cm}^{-3}$ ).

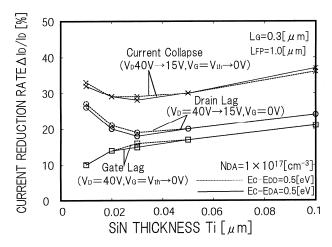

Figure 6 shows drain-current reduction rate  $\Delta I_D/I_D$  due to current collapse, drain lag or gate lag, with d as a parameter. When d is thick, the current collapse and lag phenomena are relatively large because the field plate does not almost affect the characteristics. As d becomes thinner, the current collapse and lag phenomena become smaller. This is because the buffer-trapping effects are reduced as described before. However, the rates of current collapse and drain lag increase for very thin d. This is understood that for very thin d, the electric field at the drain edge of the field plate becomes very strong, and electrons are injected deeper into the buffer layer under the field-plate region, contributing to the current collapse and drain lag. From this figure, we can say that there is an optimum thickness of SiN to minimize the buffer-related current collapse and drain lag in AlGaN/GaN HEMTs. As in Fig.5, It is also seen that the characteristics are quite similar between the two cases with different types of buffer layers. Note that the acceptor density is the same for the two cases ( $N_{\rm DA} = 10^{17}$  $cm^{-3}$ ).

Figure 4: Steady-state *I-V* curves ( $V_G = 0$  V; solid lines) and quasi-pulsed *I-V* curves (x, \*) of AlGaN/GaN HEMTs. (a) Without a field plate, (b) with 1 µm-length field plate. (\*): Only  $V_D$  is changed from 40V ( $t = 10^{-9}$  s), (x):  $V_D$  is lowered from 40 V and  $V_G$  is changed from  $V_{th}$  to 0 V ( $t = 10^{-9}$  s).

Figure 5: Current reduction rate  $\Delta I_D/I_D$  due to current collapse, drain lag or gate lag for AlGaN/GaN HEMTs, with the field-plate length  $L_{\rm FP}$  as a parameter.

#### **6** CONCLUSION

Two-dimensional transient simulations of field-plate AlGaN/GaN HEMTs with a semi-insulating buffer layer have been performed, where a deep acceptor above the

Figure 6: Current reduction rate  $\Delta I_D/I_D$  due to current collapse, drain lag or gate lag for AlGaN/GaN HEMTs, with SiN thickness *d* as a parameter. N<sub>DA</sub> = 10<sup>17</sup> cm<sup>-3</sup>.

midgap is considered. The results are compared with the case where a deep acceptor located below the midgap is compensated by a deep donor located above the midgap. It has been shown that the drain lag and current collapse could be reduced by introducing a field plate, as in the case with the deep acceptor compensated by the deep donor. This reduction occurs because electron trapping by the deep acceptors is weakened by the field plate because the electric field at the drain edge of the gate is reduced. The dependence on the field-plate length and the insulator thickness under the field plate is also studied, showing that the rates of lags and current collapse are quantitatively similar between the two cases with different types of buffer layers when the deep-acceptor density in the buffer layer is the same.

#### REFERENCES

- S. C. Binari, P. B. Klein and T. E. Kazior, "Trapping effects in GaN and SiC Microwave FETs", Proc. IEEE, vol.90, pp.1048-1058, 2002.

- [2] U. K. Mishra, L. Shen, T. E. Kazior, and Y.-F. Wu, "GaN-based RF power devices and amplifiers", Proc. IEEE, vol.96, pp.287-305, 2008.

- [3] G. Meneghesso, G. Verzellesi, R. Pierobon, F. Rarnpazzo, A. Chini, U. K. Mishra, C. Canali and E. Zanoni, "Surface-related drain current dispersion effects in AlGaN/GaN HEMTs", IEEE Trans. Electron Devices, vol.51, pp.1554-1561, 2004.

- [4] A. Koudymov, V. Adivarahan, J, Yang, G. Simon and M. A. Khan, "Mechanism of current collapse removal in field-plated nitride HFETs", IEEE Electron Device Lett., vol.26, pp.704-706, 2005.

- [5] J. Tirado, J. L. Sanchez-Rojas and J. I. Izpura, "Trapping Effects in the transient response of AlGaN/GaN HEMT devices", IEEE Trans. Electron Devices, vol.54, pp.410-417, 2007.

- [6] K. Horio, K. Yonemoto, H. Takayanagi and H. Nakano, "Physics-based simulation of buffertrapping effects on slow current transients and current collapse in GaN field effect transistors" J. Appl. Phys., vol.98, pp.124502 1-7, 2005.

- [7] K. Horio and A. Nakajima, "Physical mechanism of buffer-related current transients and current slump in AlGaN/GaN high electron mobility transistors", Jpn. J. Appl. Phys., vol.47, pp.3428-3433, 2008.

- [8] M. Faqir, G. Verzellesi, G. Meneghesso, E. Zanoni, and F. Fantini, "Investigation of high-electric-field degradation effects in AlGaN/GaN HEMTs", IEEE Trans. Electron Devices, vol.55, pp.1592-1602, 2008.

- [9] K. Horio, A. Nakajima, and K. Itagaki, "Analysis of field-plate effects on buffer-related lag phenomena and current collapse in GaN MESFETs and AlGaN/GaN HEMTs", Semicond. Sci. Technol., vol.24, pp.085022-1–085022-7, 2009.

- [10] K. Horio, H. Onodera, and A. Nakajima, "Analysis of backside-electrode and gate-field-plate effects on buffer-related current collapse in AlGaN/GaN high electron mobility transistors", J. Appl. Phys., vol.109, pp.114508-1–114508-7, 2011.

- [11] M. Silvestri, M. J. Uren and M. Kuball, "Ironinduced deep-acceptor center in GaN/AlGaN high electron mobility transistors: Energy level and cross section", Appl. Phys. Lett., vol.102, pp.073051-1–073501-4, 2013.

- [12] K. Horio, H. Yanai and T. Ikoma, "Numerical simulation of GaAs MESFET's on the semiinsulating substrate compensated by deep traps", IEEE Trans. Electron Devices, vol.35, pp.1778-1785, 1988.

- [13] K. Horio and T. Yamada, "Two-dimensional analysis of surface-state effects on turn-on characteristics in GaAs MESFET's", IEEE Trans. Electron Devices, vol.46, pp.648-655, 1999.

- [14] K. Horio, A. Wakabayashi and T. Yamada, "Twodimensional analysis of substrate-trap effects on turn-on characteristics in GaAs MESFET's", IEEE Trans. Electron Devices, vol.47, pp.617-624, 2000.

- [15] A. Wakabayashi, Y. Mitani and K. Horio, "Analysis of gate-lag phenomena in recessed-gate and buried-gate GaAs MESFETs", IEEE Trans. Electron Devices, vol.49, pp.37-41, 2002.

- [16] K. Horio, T. Tanaka, K. Itagaki and A. Nakajima, "Two-dimensional analysis of field-plate effects on surface state-related current transients and power slump in GaAs FETs", IEEE Trans. Electron Devices, vol.58, pp. 698-703, 2011.

- [17] A. Nakajima, K. Fujii and K. Horio, "Numerical analysis of buffer-trap effects on gate lag in AlGaN/GaN high electron mobility transistors", Jpn. J. Appl. Phys., vol.50, pp.104303-1–104303-6, 2011.