# Simulation of Current Slump Removal in Field-Plate GaAs MESFETs

A. Nomoto, Y. Sato and K. Horio

Faculty of Systems Engineering, Shibaura Institute of Technology 307 Fukasaku, Minuma-ku, Saitama 337-8570, Japan, horio@sic.shibaura-it.ac.jp

### ABSTRACT

Two-dimensional transient analysis of field-plate GaAs MESFETs is performed by considering surface states in the region from the gate toward the drain. The field-plate length  $L_{\rm FP}$  and the thickness of SiO<sub>2</sub> passivation layer *d* are varied as parameters. It is shown that the drain lag and current slump are reduced by introducing a field plate longer than the length of surface-state region  $L_{\rm S}$ , but they are not removed completely when *d* is thick. It is clearly shown that when *d* becomes very thin ( $\leq 0.02 \,\mu$ m), the lags and current slump are completely removed for  $L_{\rm FP}$  longer than  $L_{\rm S}$ . By carefully examining the  $L_{\rm FP}$  dependence for  $d = 0.02 \,\mu$ m, it is found that they are completely removed even if  $L_{\rm FP}$  is comparable to  $L_{\rm S}$ .

Keywords: GaAs FET, current slump, surface state, drain lag, gate lag

#### **1 INTRODUCTION**

In compound semiconductor FETs, slow current transients are often observed even if the drain voltage or the gate voltage is changed abruptly [1,2]. This is called drain lag or gate lag, and undesirable for circuit applications. Slow transients indicate that dc and RF current-voltage (I-V) curves become quite different, resulting in lower RF power available than that expected from dc operation [3]. This is called current slump. These phenomena occur due to surface states and/or bulk traps [1-5]. Experimentally, the introduction of field plate like Fig.1 is shown to reduce the lags and current slump [3,6,7]. However, few simulation studies on field-plate structures have been made, although GaN-based FETs with bulk traps are studied [8]. In previous works [9,10], we made two-dimensional analysis of field-plate GaAs MESFETs including surface states, and showed that surface-related lags and current slump could be reduced by introducing a field plate and that in some cases, they were completely removed. In this work, we have further studied the field-plate effects and studied the condition when the lags and current collapse are completely removed.

## **2** PHYSICAL MODELS

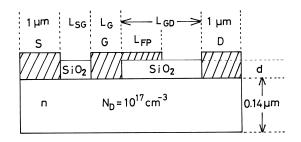

Figure 1 shows a device structure analyzed in this study. The gate length  $L_{\rm G}$  is typically set to 0.3 µm. The gate

Figure 1: Device structure analyzed in this study.

electrode extends on to SiO2 passivation layer. This is called a field plate. The field-plate length  $L_{\rm FP}$  is varied as a parameter. The thickness of  $SiO_2$  layer d is also varied. Relatively high densities of surface states are considered only at the drain edge of the gate region. This situation can occur after the device has been stressed or due to device degradation. Here the length of surface-state region  $L_{\rm S}$  is set to 0.4 µm from the gate edge toward the drain. As a surface-state model, we adopt Spicer's unified defect model, and assume that the surface states consist of a pair of a deep donor and a deep acceptor. The surface states are assumed to distribute uniformly within 5 Å from the surface, and their densities ( $N_{SD}$ ,  $N_{DA}$ ) are typically set to  $6 \times 10^{19}$  cm<sup>-3</sup>  $(3x10^{12} \text{ cm}^{-2})$ . As for their energy levels, the following case based on experiments is considered as in a previous work [9,10]:  $E_{SD} = 0.87$  eV,  $E_{SA} = 0.7$  eV, where  $E_{SD}$  is the energy difference between the bottom of conduction band and the deep donor's energy level, and  $E_{SA}$  is the energy difference between the deep acceptor's energy level and the top of valence band. In this case, the deep-acceptor surface state mainly determines the surface Fermi level, and it acts as a hole trap.

Basic equations to be solved are Poisson's equation including ionized deep-level terms, continuity equations for electrons and holes which include carrier loss rates via the deep levels, and rate equations for the deep levels [11-14]. These are expressed as follows.

1) Poisson's equation

$$\nabla^2 \psi = -\frac{q}{\varepsilon} (p - n + N_{\rm D} + N_{\rm Di} + N_{\rm SD}^+ - N_{\rm SA}^-) \tag{1}$$

2) Continuity equations for electrons and holes

$$\frac{\partial n}{\partial t} = \frac{1}{q} \nabla \bullet J_n - (R_{n,\text{SD}} + R_{n,\text{SA}})$$

(2)

$$\frac{\partial p}{\partial t} = -\frac{1}{q} \nabla \bullet J_p - (R_{p,\text{SD}} + R_{p,\text{SA}})$$

(3)

where

$$R_{n,\rm SD} = C_{n,\rm SD} N_{\rm SD}^+ n - e_{n,\rm SD} (N_{\rm SD} - N_{\rm SD}^+)$$

(4)

$$R_{n,SA} = C_{n,SA} (N_{SA} - N_{SA}^{-}) n - e_{n,SA} N_{SA}^{-}$$

(5)

$$R_{p,\rm SD} = C_{p,\rm SD} (N_{\rm SD} - N_{\rm SD}^{+}) p - e_{p,\rm SD} N_{\rm SD}^{+}$$

(6)

$$R_{p,SA} = C_{p,SA} N_{SA}^{-} p - e_{p,SA} (N_{SA} - N_{SA}^{-})$$

(7)

3) Rate equations for the deep levels

$$\frac{\partial}{\partial t}(N_{\rm SD} - N_{\rm SD}^+) = R_{n,\rm SD} - R_{p,\rm SD}$$

(8)

$$\frac{\partial}{\partial t}N_{\rm SA}^{-} = R_{n,\rm SA} - R_{p,\rm SA} \tag{9}$$

where  $N_{SD}^+$  and  $N_{SA}^-$  are ionized densities of surface deep donors and surface deep acceptors, respectively.  $C_n$  and  $C_p$ are electron and hole capture coefficients of the deep levels, respectively,  $e_n$  and  $e_p$  are electron and hole emission rates of the deep levels, respectively, and the subscript (SD, SA) represents the corresponding deep level.

These equations are put into discrete forms and are solved numerically. We have calculated the drain-current responses when the drain voltage  $V_{\rm D}$  and/or the gate voltage  $V_{\rm G}$  are changed abruptly.

# 3 SLOW CURRENT TRANSIENTS (DRAIN LAG)

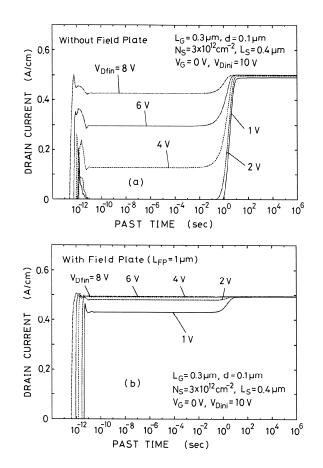

Figure 2 shows calculated drain-current responses of GaAs MESFETs considering surface states when  $V_D$  is lowered abruptly from 10 V to  $V_{\text{Dfin}}$ , where  $V_{\text{G}}$  is kept constant at 0 V. Here, the surface-state density is  $3x10^{12}$ cm<sup>-2</sup>, and the surface-state length  $L_{\rm S}$  is 0.4 µm.. Fig.2(a) shows a case without a field plate, and Fig.2(b) shows a case with a field plate ( $L_{\rm FP} = 1 \ \mu m$ ). The thickness of SiO<sub>2</sub> layer d is 0.1  $\mu$ m. In both cases, the drain current  $I_D$  remains at a low value for some periods  $(10^{-10} - 10^{-1} \text{ s})$  and begins to increase slowly, showing drain lag behavior. It is understood that the drain current begins to increase when the deep-acceptor surface states begin to capture holes [11] or emit electrons. It is clearly seen that the change of drain current is smaller for the case with a field plate when comparing for the same  $V_{\text{Dfin}}$ , indicating that the drain lag is smaller for the field-plate structure. Without a field plate, a barrier for electrons is formed at the gate-to-drain region during the transients [9], and hence  $I_{\rm D}$  becomes very low. On the other hand, with a field plate, the potential under the field plate is almost flat and a small barrier is seen at the field-plate edge, and hence  $I_D$  becomes larger, resulting in

Figure 2: Calculated drain-current responses of GaAs MESFETs when  $V_D$  is lowered abruptly from 10 V to  $V_{Dfin}$  and  $V_G$  is kept constant at 0 V.  $d = 0.1 \,\mu\text{m}$ .  $N_S = 3 \times 10^{12} \,\text{cm}^{-2}$  and the surface-state layer length  $L_S$  is 0.4  $\mu\text{m}$ . (a) Without field plate, (b) with field plate ( $L_{FP} = 1 \,\mu\text{m}$ ).

smaller drain lag.

### 4 TURN-ON CHARACTERISTICS AND CURRENT SLUMP

Next, we have calculated a case when  $V_{\rm G}$  is also changed from an off point.  $V_{\rm G}$  is changed from the threshold voltage  $V_{\rm th}$  to 0 V, and  $V_{\rm D}$  is lowered from 10 V to  $V_{\rm Don}$  (on-state drain voltage).  $V_{\rm th}$  is defined here as a gate voltage where the drain current  $I_{\rm D}$  becomes  $5 \times 10^{-3}$  A/cm. The characteristics (not shown here) become similar to those shown in Fig.2, although some transients arise when only  $V_{\rm G}$  is changed (gate lag), and hence the current reduction rate becomes higher than that of drain lag. This current reduction is called current slump which is a combined effect of drain lag and gate lag.

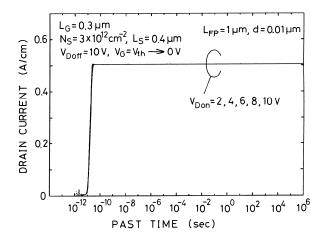

Figure 3 shows calculated turn-on characteristics when  $L_{\rm FP} = 1 \ \mu m$  and *d* is very thin (0.01  $\mu m$ ). Here,  $V_{\rm D}$  is lowered from 10 V to  $V_{\rm Don}$  and  $V_{\rm G}$  is changed from  $V_{\rm th}$  to 0 V. Surprisingly, the slow current transients disappear,

Figure 3: Calculated turn-on characteristics for  $L_{\rm FP} = 1 \ \mu m$  and  $d = 0.01 \ \mu m$  when  $V_{\rm D}$  is lowered abruptly from 10 V to  $V_{\rm Don}$  and  $V_{\rm G}$  is changed from  $V_{\rm th}$  to 0 V.  $N_{\rm S} = 3 \times 10^{12} \ {\rm cm}^{-2}$  and  $L_{\rm S} = 0.4 \ \mu m$ .

indicating that the lags and current slump are completely removed in this case. This may be because the surface-state effects are completely masked by the field plate.

## 5 FIELD-PLATE PARAMETER DEPENDENCE AND REMOVAL OF CURRENT SLUMP

We have next studied dependence of lag phenomena and current slump on the field-plate length  $L_{\text{FP}}$  and on the SiO<sub>2</sub> layer thickness *d*.

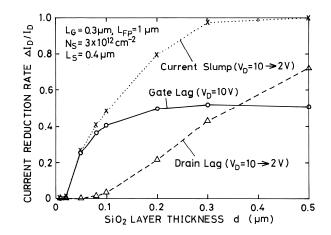

Figure 4 shows current reduction rates  $\Delta I_D/I_D$  due to current slump, drain lag, or gate lag, with *d* as a parameter. Here  $L_{\rm FP} = 1 \,\mu m$ . As *d* becomes thin, the lags and current slump are reduced, and they are completely removed when *d* becomes thinner than 0.02  $\mu m$ . This may be because surface-state effects are completely masked by the field plate. When *d* is thin, the gate parasitic capacitance becomes a problem, but this removal of current slump is still a very interesting result.

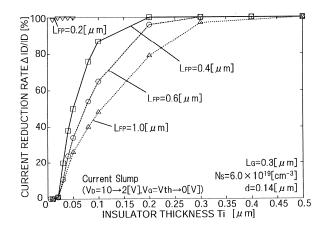

Figiure 5 shows current reduction rates  $\Delta I_D/I_D$  due to current slump as a function of SiO<sub>2</sub> layer thickness *d*, with field-plate length  $L_{\rm FP}$  as a parameter. It is seen that when  $L_{\rm FP}$  becomes shorter, the current slump becomes larger, but it is completely removed when *d* becomes thinner than 0.02 µm even if  $L_{\rm FP}$  is equal to the surface-state layer length  $L_{\rm S}$ (0.4 µm), although the current slump becomes very large when  $L_{\rm FP} = 0.2$  µm.

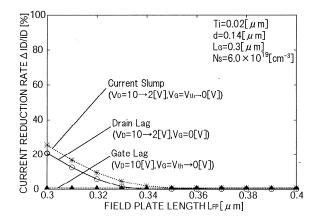

In order to study how short we can reduce the field-plate length  $L_{\rm FP}$  while maintaining the removal of current slump, we calculate in detail the lags and current slump between  $L_{\rm FP} = 0.3 \,\mu\text{m}$  and 0.4  $\mu\text{m}$  in the case of  $d = 0.02 \,\mu\text{m}$ . Figure 6 shows the results. From this figure, we can conclude that the current slump is completely removed even if  $L_{\rm FP}$  is shortened to 0.35  $\mu\text{m}$ .

Figure 4: Current reduction rate  $\Delta I_D/I_D$  due to current slump, drain lag or gate lag as a function of SiO<sub>2</sub> layer thickness *d* in the case of  $L_{\rm FP} = 1 \ \mu \text{m}$ .  $N_{\rm S} = 3 \times 10^{12} \text{ cm}^{-2}$  and  $L_{\rm S} = 0.4 \ \mu \text{m}$ .

Figure 5: Current reduction rate  $\Delta I_D/I_D$  due to current slump, as a function of SiO<sub>2</sub> layer thickness *d*, with field-plate length  $L_{\rm FP}$  as a parameter.  $N_{\rm S} = 3 \times 10^{12}$  cm<sup>-2</sup> and  $L_{\rm S} = 0.4$  µm.

Figure 6: Current reduction rate  $\Delta I_D/I_D$  due to current slump, drain lag or gate lag as a function of field-plate length  $L_{\rm FP}$  (0.3 ~ 0.4 µm) in the case of d = 0.02 µm.  $N_{\rm S} = 3 \times 10^{12}$  cm<sup>-2</sup> and  $L_{\rm S} = 0.4$  µm.

### 6 CONCLUSION

Two-dimensional transient analysis of field-plate GaAs MESFETs has been performed by considering surface states in the region from the gate toward the drain. The field-plate length  $L_{\rm FP}$  and the thickness of SiO<sub>2</sub> passivation layer *d* are varied as parameters. It has been shown that the drain lag and current slump are reduced by introducing a field plate longer than the length of surface-state region  $L_{\rm S}$ , but they are not removed completely when *d* is thick. It has been clearly shown that when *d* becomes very thin ( $\leq 0.02 \mu$ m), the lags and current slump are completely removed for  $L_{\rm FP}$  longer than  $L_{\rm S}$ . By carefully examining the  $L_{\rm FP}$  dependence for  $d = 0.02 \mu$ m, it has been found that the lags and current slump are completely removed even if  $L_{\rm FP}$  is comparable to  $L_{\rm S}$ .

#### REFERENCES

- [1] J. C. Huang, G. S. Jackson, S. Shanfield, A. Platzker, P. K. Saledas, and C. Weichert, "An AlGaAs/InGaAs pseudomorphic high electron mobility transistor with improved breakdown voltage for X- and Ku-band power applications", IEEE Trans. Microwave Theory Tech., vol.41, pp.752-759, 1993.

- [2] S. C. Binari, P. B. Klein, and T. E. Kazior, "Trapping effects in GaN and SiC microwave FETs", Proc. IEEE, vol.90, pp.1048-1058, 2002.

- [3] U. K. Mishra, L. Shen, T. E. Kazior, and Y.-F. Wu, "GaN-based RF power devices and amplifiers", Proc. IEEE, vol.96, pp.287-305, 2008.

- [4] G. Koley, V. Tilak, L. F. Eastman and M. G. Spencer, "Slow transients observed in AlGaN/GaN HFETs: Effects of SiN<sub>x</sub> passivation and UV illumination", IEEE Trans. Electron Devices, vol.50, pp.886-893, 2003.

- [5] V. Desmaris, M. Rudzinski, N. Rorsman, P. R. Hageman, P. K. Larsen, H. Zirath, T. C. Rodle, and H. F. F. Jos, "Comparison of the dc and microwave performance of AlGaN/GaN HEMTs grown on SiC by MOCVD with Fe-doped or unintentionally

doped GaN buffer layers", IEEE Trans. Electron Devices, vol.53, pp.2413-2417, 2006.

- [6] A. Koudymov, V. Adivarahan, J, Yang, G. Simon, and M. A. Khan, "Mechanism of current collapse removal in field-plated nitride HFETs", IEEE Electron Device Lett., vol.26, pp.704-706, 2005.

- [7] W. Saito, T. Nitta, Y. Kakiuchi, Y. Saito, K. Tsuda, I. Omura, and M. Yamaguchi, "Suppression of dynamic on-resistance increase and gate charge measurements in high-voltage GaN-HEMTs with optimized field-plate structure", IEEE Trans. Electron Devices, vol54, pp.1825-1830, 2007.

- [8] K. Horio, A. Nakajima, and K. Itagaki, "Analysis of field-plate effects on buffer-related lag phenomena and current collapse in GaN MESFETs and AlGaN/GaN HEMTs", Semicond. Sci. Technol., vol. 24, pp.085022-1–085022-7, 2009.

- [9] K. Horio, T. Tanaka, K. Itagaki and A. Nakajima, "Two-dimensional analysis of field-plate effects on surface state-related current transients and power slump in GaAs FETs", IEEE Trans. Electron Devices, vol.58, pp. 698-703, 2011.

- [10] H. Hafiz, M. Kumeno, and K. Horio, "Analysis of removal of surface-state-related lags and current slump in GaAs FETs", IEEE Electron Device Lett., vol.34, pp.1361-1363, 2013.

- [11] K. Horio, H. Yanai and T. Ikoma, "Numerical simulation of GaAs MESFET's on the semiinsulating substrate compensated by deep traps", IEEE Trans. Electron Devices, vol.35, pp.1778-1785, 1988.

- [12] K. Horio and T. Yamada, "Two-dimensional analysis of surface-state effects on turn-on characteristics in GaAs MESFET's", IEEE Trans. Electron Devices, vol.46, pp.648-655, 1999.

- [13] K. Horio, A. Wakabayashi and T. Yamada, "Twodimensional analysis of substrate-trap effects on turn-on characteristics in GaAs MESFET's", IEEE Trans. Electron Devices, vol.47, pp.617-624, 2000.

- [14] A. Wakabayashi, Y. Mitani and K. Horio, "Analysis of gate-lag phenomena in recessed-gate and buried-gate GaAs MESFETs", IEEE Trans. Electron Devices, vol.49, pp.37-41, 2002.