# Suppression of Variability in Metal Source/Drain SOI MOSFET with Partial Buried Oxide and δ-doping

Ganesh C. Patil and S. Qureshi

Department of Electrical Engineering, Indian Institute of Technology Kanpur, Kanpur-208016, India, pganesh@iitk.ac.in, qureshi@iitk.ac.in

# ABSTRACT

Recently, metal source/drain (S/D) dopant-segregated Schottky barrier (DSSB) SOI MOSFET has attracted the attention of researchers due to its planar structure, CMOS compatibility and reduced S/D series resistance at thin silicon film. However, at nanoscale the inhomogeneity in Schottky barrier height and segregation length increases the device parameter variations. To alleviate this problem, in this work it has been shown that, employing partial buried oxide only under the metal S/D and  $\delta$ -doping under the channel suppresses the variability in DSSB SOI MOSFET. In addition, for the first time, the impact of variability on digital/analog circuit performance metrics such as leakage power dissipation, intrinsic gate delay, cut-off frequency and open-circuit voltage gain has been investigated.

*Keywords*: Schottky barrier, variability, partial buried oxide, SOI MOSFET, digital/analog circuit performance

### **1 INTRODUCTION**

Due to CMOS compatibility, low-source/drain (S/D) series resistance, improved scalability and better shortchannel effect immunity dopant-segregated Schottky barrier (DSSB) silicon-on-insuator (SOI) MOSFET has been widely studied as a potential work horse for meeting the challenges at the end of semiconductor technology roadmap [1]-[6]. However, it has been shown that, employing dopant-segregation during silicidation leads to an increase in the device parameter variations and the inhomogeneity in Schottky barrier (SB) height ( $\Phi_{bn}$ ) affects the saturation threshold voltage  $(V_{\text{TSAT}})$  of the device [7]-[9]. To address this problem, in this work it has been shown that, employing partial buried oxide and p-type  $\delta$ -doping under the epitaxial channel of DSSB SOI MOSFET suppresses the device parameter variations induced by the process fluctuations in dopant segregation length ( $L_{DSL}$ ),  $\Phi_{bn}$  and silicon film thickness  $(T_{\rm Si})$  of the device.

Furthermore, the impact of variability on digital/analog circuit performance metrics such as leakage power dissipation ( $I_{OFF}$ . $V_{DD}$ ), intrinsic gate delay ( $C_G$ . $V_{DD}$ / $I_{ON}$ ), cut-off frequency ( $f_t$ ) and open-circuit voltage gain ( $A_{Vopen}$ ) of DSSB SOI and the proposed  $\delta$ -doped partially-insulated DSSB (DSSB Pi-OX- $\delta$ ) MOSFETs has been investigated. Here,  $I_{OFF}$ ,  $I_{ON}$ ,  $C_G$  and  $V_{DD}$  represents the off-state leakage current, on-state drive current, gate capacitance and the supply voltage respectively.

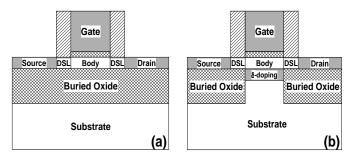

Figure 1: (a) DSSB SOI and (b) DSSB Pi-OX-δ MOSFETs used in MEDICI simulations.

The organization of rest of the paper is as follows, Section 2 presents the device structures and the simulation methodology used in this work whereas Section 3 presents the detailed discussion on process induced device parameter variations and the impact of variability on digital/analog circuit metrics of DSSB SOI and DSSB Pi-OX- $\delta$ MOSFETs. Finally the conclusion is given in Section 4.

# 2 DEVICE STRUCTURES AND SIMULATION SETUP

The device structures and the parameters used in the MEDICI simulator [10] are shown in Fig. 1 and Table 1 respectively. The range of physical gate length ( $L_G$ ) and the gate oxide thickness have been considered as per the requirements specified in ITRS-2009 [6]. The segregation length i.e.  $L_{DSL}$  has been considered as the distance between the metal-semiconductor (M-S) junction edge and the p-n junction edge where the doping in the segregation layer drops to  $1 \times 10^{15}$  cm<sup>-3</sup>.

Since carriers in the channel are mainly transported due to drift-diffusion and at the M-S junction are due to tunneling, both drift-diffusion and SB tunneling models have been incorporated along with the mobility models. Further, to extract the analog figures of merit for both DSSB SOI and proposed DSSB Pi-OX- $\delta$  MOSFETs, the small-signal ac analysis by considering source as a ground terminal has been carried out [3]-[5]. In order to study the impact of process fluctuations in  $L_{DSL}$ ,  $\Phi_{bn}$  and  $T_{Si}$  different sets of devices with varying  $L_{DSL}$ ,  $\Phi_{bn}$  and  $T_{Si}$  have been simulated. The standard deviations ( $\sigma$ ) obtained in each set of 25 devices for  $L_{DSL}$ ,  $\Phi_{bn}$  and  $T_{Si}$  are 1.8 nm, 0.06 eV and 1.3 nm respectively [5]. The detailed fabrication steps of the proposed DSSB Pi-OX- $\delta$  MOSFET can be seen in [3].

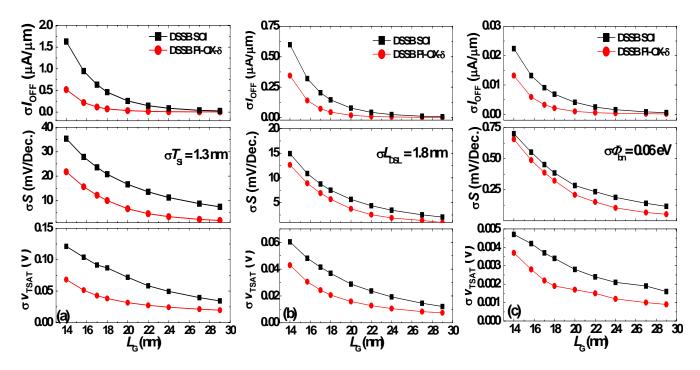

Figure 2: Variation of  $\sigma V_{\text{TSAT}}$ ,  $\sigma S$  and  $\sigma I_{\text{OFF}}$  with physical gate length showing the impact of process induced fluctuations in (a)  $T_{\text{Si}}$ , (b)  $L_{\text{DSL}}$  and (c)  $\Phi_{\text{bn}}$  of DSSB SOI and DSSB Pi-OX- $\delta$  MOSFETs.

| Parameter                                                                   | DSSB<br>SOI        | DSSB<br>Pi-OX-δ    |

|-----------------------------------------------------------------------------|--------------------|--------------------|

| Physical gate length (nm)                                                   | variable           | variable           |

| Gate oxide thickness (nm)                                                   | 1                  | 1                  |

| Nominal Silicon film thickness<br>(nm)                                      | 8                  | 8                  |

| Buried oxide thickness (nm)                                                 | 50                 | 50                 |

| Substrate thickness (nm)                                                    | 100                | 100                |

| Spacer thickness (nm)                                                       | 10                 | 10                 |

| Doping in segregation layer (cm <sup>-3</sup> )                             | $1 \times 10^{20}$ | 1×10 <sup>20</sup> |

| Channel doping (cm <sup>-3</sup> )                                          | 1×10 <sup>15</sup> | 1×10 <sup>15</sup> |

| Substrate doping (cm <sup>-3</sup> )                                        | 1×10 <sup>15</sup> | 1×10 <sup>15</sup> |

| Nominal dopant-segregation layer<br>length (nm)                             | 11                 | 11                 |

| Nominal electron SB height (eV)                                             | 0.3                | 0.3                |

| Nominal hole SB height (eV)                                                 | 0.82               | 0.82               |

| p-type $\delta$ -layer doping density under the channel (cm <sup>-3</sup> ) | #                  | 3×10 <sup>18</sup> |

| Thickness of p-type $\delta$ -layer under the channel (nm)                  | #                  | 10                 |

| Supply voltage (V)                                                          | 1                  | 1                  |

| Saturation threshold voltage (V)                                            | 0.2                | 0.2                |

Table 1: Device parameters used in the MEDICI simulations.

#### **3** RESULTS AND DISCUSSION

# 3.1 Process Induced Device Parameter Variations

The comparison of standard deviations in  $V_{\text{TSAT}}$ , subthreshold swing (S) and  $I_{\text{OFF}}$  as a function of  $L_{\text{G}}$  for DSSB SOI and the proposed DSSB Pi-OX- $\delta$  MOSFETs is shown in Fig. 2. The  $V_{\text{TSAT}}$  is defined as the gate voltage at which

$$I_{\rm D} = 1 \times 10^{-7} \left(\frac{W}{L_{\rm G}}\right),\tag{1}$$

where  $W = 1 \ \mu m$  is the width of the transistor. Further, S has been extracted at  $V_{\text{DS}} = 1 \ \text{V}$  whereas  $I_{\text{OFF}}$  has been extracted at  $V_{\text{DS}} = V_{\text{DD}} = 1 \ \text{V}$  and  $V_{\text{GS}} = V_{\text{GOFF}} = 0 \ \text{V}$ .

From Fig. 2 it can be clearly seen that, the variations in  $V_{\text{TSAT}}$ , *S* and  $I_{\text{OFF}}$  due to  $T_{\text{Si}}$ ,  $L_{\text{DSL}}$  and  $\Phi_{\text{bn}}$  fluctuations in both DSSB SOI and DSSB Pi-OX- $\delta$  MOSFETs are relatively small when  $L_{\text{G}}$  is more than 20 nm. However, when  $L_{\text{G}}$  is scaled down the parameter variations become more significant. Further, due to exponential dependence of device characteristics on  $T_{\text{Si}}$  [11], the variations in  $V_{\text{TSAT}}$ , *S* and  $I_{\text{OFF}}$  due to  $T_{\text{Si}}$  fluctuations are larger in comparison to  $L_{\text{DSL}}$  and  $\Phi_{\text{bn}}$  fluctuations. Moreover, since the presence of buried oxide opening under the channel reduces the stringent requirement of uniformity in thin Si film and the screening effect due to p-type  $\delta$ -doping reduces the random dopant fluctuations [11]-[12], the parameter variations in scaled DSSB Pi-OX- $\delta$  MOSFET are significantly low as compared to scaled DSSB SOI MOSFET.

## **3.2 Impact of Variability on Digital/Analog** Circuit Performance Metrics

In order to study the impact of process induced fluctuations in physical device parametres ( $T_{\rm Si}$ ,  $L_{\rm DSL}$  and  $\Phi_{\rm bn}$ ) on digital/analog circuit performance metrics such as ( $I_{\rm OFF}$ . $V_{\rm DD}$ ), ( $C_{\rm G}$ . $V_{\rm DD}/I_{\rm ON}$ ),  $f_{\rm t}$  and  $A_{\rm Vopen}$  the standard deviations in  $I_{\rm OFF}$ ,  $I_{\rm ON}$ ,  $C_{\rm G}$ ,  $A_{\rm Vopen}$  and the short-circuit current gain ( $A_{\rm ishort}$ ) has been recorded. Here,  $I_{\rm ON}$  has been extracted at  $V_{\rm DS} = V_{\rm DD}$  and  $V_{\rm GS} = V_{\rm GOFF} + V_{\rm DD}$  whereas  $C_{\rm G}$  has been extracted by summing the parasitic capacitances namely gate-to-source ( $C_{\rm gs}$ ) and gate-to-drain ( $C_{\rm gd}$ ) of the MOSFETs. The  $C_{\rm gs}$  and  $C_{\rm gd}$  are defined as [13]

$$C_{i,j} = \frac{Q_i}{V_j},\tag{2}$$

where i = g and j = s, d. and have been extracted by applying  $\frac{dQ}{dV}$  method of the MEDICI simulator at drain bias of 1 V. The cut-off frequency i.e.  $f_t$  has been extracted from the  $A_{ishort}$  which is defined as [14]

$$A_{\rm ishort} = \frac{Y_{21}}{Y_{11}},$$

(3)

whereas the open circuit voltage gain i.e.  $A_{Vopen}$  is defined as [14]

$$A_{\rm Vopen} = \frac{Y_{21}}{Y_{22}}.$$

(4)

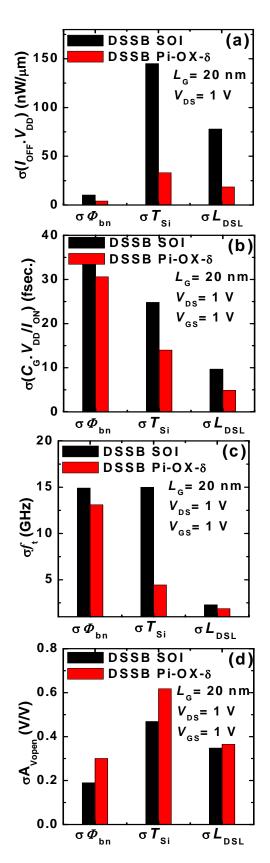

From Fig. 3(a)-(d) it can be seen that, although  $\sigma A_{Vopen}$ in the proposed DSSB Pi-OX- $\delta$  MOSFET is larger in comparison to DSSB SOI MOSFET, the ~77%, ~44% and ~70% reduction in  $\sigma(I_{OFF}.V_{DD})$ ,  $\sigma(C_G.V_{DD}/I_{ON})$  and  $\sigma f_t$ respectively makes the proposed DSSB Pi-OX- $\delta$  MOSFET suitable for fluctuation resistant digital/analog circuits.

In addition, from Fig. 3(a) it can be seen that, in comparison to  $\sigma T_{Si}$ , the standard deviation in  $I_{OFF}$ .  $V_{DD}$  due to  $\sigma \Phi_{bn}$  and  $\sigma L_{DSL}$  is lower. Further, from Fig. 3(b)-(c) it can be seen that, the standard deviation in  $(C_G.V_{DD})/I_{ON}$  and  $f_t$  due to  $\sigma L_{DSL}$  is lower in both the devices. From these results, it can be clearly seen that, among all the process induced fluctuations (i.e.  $\sigma \Phi_{bn}$ ,  $\sigma T_{Si}$  and  $\sigma L_{DSL}$ ) the intrinsic digital/analog circuit performance of DSSB SOI MOSFET is mainly affected by the fluctuations in  $T_{Si}$ . Thus, although the fluctuations in  $\Phi_{bn}$  and  $L_{DSL}$  of DSSB SOI MOSFET can leads to an increase in the device parameter variations, the main source of variability of this device is the  $T_{Si}$  fluctuations, which can be significanly suppressed by employing the partial buried oxide and  $\delta$ -doping under the channel of this device.

#### 4 CONCLUSIONS

In this work, a comprehensive study on process induced variability in DSSB SOI MOSFET has been carried out by using the two dimensional MEDICI simulator. It has been shown that, employing partial buried oxide only under the S/D and p-type  $\delta$ -doping under the epitaxial channel of

Figure 3: Comparision of standard deviation in (a)  $I_{\text{OFF}}.V_{\text{DD}}$  (b)  $(C_{\text{G}}.V_{\text{DD}})/I_{\text{ON}}$  (c)  $f_{\text{t}}$  and (d)  $A_{\text{Vopen}}$  due to process induced fluctuations in  $\Phi_{\text{bn}}$ ,  $T_{\text{Si}}$  and  $L_{\text{DSL}}$  of DSSB SOI and DSSB Pi-OX- $\delta$  MOSFETs.

DSSB SOI MOSFET suppresses the process induced variability of this device. The impact of variability on digital/analog circuit performance metrics of DSSB SOI and the proposed DSSB Pi-OX- $\delta$  MOSFETs has also been investigated. It has been found that, although  $\sigma A_{Vopen}$  in the proposed DSSB Pi-OX- $\delta$  MOSFET is larger in comparison to DSSB SOI MOSFET, the significant reduction in  $\sigma(I_{OFF}.V_{DD})$ ,  $\sigma(C_G.V_{DD}/I_{ON})$  and  $\sigma f_t$  makes the proposed device suitable for fluctuation resistant digital/analog circuits.

#### REFERENCES

- M. Zhang, J. Knoch, Q. T. Zhao, U. Breuer and S. Mantl, "Impact of dopant segregation on fully depleted Schottky-barrier SOI-MOSFETs", Solid-State Electronics, 50, 594-600, 2006.

- [2] S.-J. Choi, C.-J. Choi, J.-Y. Kim, M. Jang, and Y.-K. Choi, "Analysis of Transconductance (g<sub>m</sub>) in Schottkybarrier MOSFETs", IEEE Trans. Electron Devices, 58, 427-432, 2011.

- [3] G. C. Patil and S. Qureshi, "A novel δ-doped partially insulated dopant-segregated Schottky barrier SOI MOSFET for analog/RF applications", Semiconductor Science and Technology 26, 085002, 2011.

- [4] G. C. Patil and S. Qureshi, "Underlap channel metal source/drain SOI MOSFET for thermally efficient lowpower mixed-signal circuits", Microelectronics Journal, 43, 321-328, 2012.

- [5] G. C. Patil and S. Qureshi, "Engineering spacers in dopant-segregated Schottky barrier SOI MOSFET for nanoscale CMOS logic circuits", Semiconductor Science and Technology, 27, 045004, 2012.

- [6] International Technology Roadmap for Semiconductor (ITRS), 2009, [Online]. Available: <u>http://public.itrs.net</u>.

- [7] M. Zhang, J. Knoch, S.-L. Zhang, S. Feste, M. Schroter and S. Mantl, "Threshold voltage variations in SOI Schottky-barrier MOSFETs", IEEE Trans. Electron Devices, 55, 858-865, 2008.

- [8] S. F. Feste, M. Zhang, J. Knoch and S. Mantl, "Impact of variability on the performance of SOI Schottky barrier MOSFETs", Solid-State Electronics, 53, 418-423, 2009.

- [9] S. F. Feste, M. Zhang, J. Knoch, S.-L Zhang and S. Mantl, "Variability in SOI Schottky barrier MOSFETs", in Proc. Ultimate Integration of Silicon, 27-30, 2008.

- [10] MEDICI User Manual, Ver. Y-2006.06, TMA, 2006.

- [11] Y. Tian, H. Xiao, R. Huang, C. Feng, M. Chan, B. Chen, R. Wang, X. Zhang, and Y. Wang, "Quasi-SOI MOSFETs – A promising bulk device candidate for extremely scaled era", IEEE Trans. Electron Devices, 54, 1784-1788, 2007.

- [12] A. Asenov and S. Saini, "Suppression of random dopant-induced threshold voltage fluctuations in sub-0.1-μm MOSFETs with epitaxial and δ-doped

channels", IEEE Trans. Electron Devices, 46, 1718-1724, 1999.

- [13] O. Moldovan, F. A. Chaves, D. Jiménez and B. Iñiguez, "Compact charge and capacitance modeling of undoped ultra-thin body (UTB) SOI MOSFETs", Solid-State Electronics, 52, 1867-1871, 2008.

- [14] S. Eminente, N. Barin, P. Palestri, C. Fiegna and E. Sangiorgi, "Small-signal analysis of Decananometer bulk and SOI MOSFETs for Analog/Mixed-signal and RF applications using the time-dependent Monte Carlo approach", IEEE Trans. Electron Devices, 54, 2283-2292, 2007.