# Field-Based 3D Capacitance Modeling for sub-45-nm On-Chip Interconne

Aixi Zhang<sup>1,2</sup>, Wei Zhao<sup>1</sup>, Yun Ye<sup>1</sup>, Jin He<sup>1</sup>, Aixin Chen<sup>2</sup>, and Mansun Chan<sup>3</sup>

#### **ABSTRACT**

Considering both two-dimensional and three-dimensional single wire above plate, the proposed method decomposes the electric field into various regions and gives solutions for each part. The total ground capacitance is the summation of all components. The solution can be easily extended to the case of two parallel wires. Its physical base minimizes the complexity and error in a traditional model fitting process. The new compact model accurately predicts the capacitance value, compared to the COMSOL simulations, for not only the nominal wire dimensions from the latest ITRS updates, but also a wide range of other back-end-of-the-line dimensions.

**Keywords**: Capacitance modeling, fringe capacitance, terminal capacitance, electric field, interconnect.

# I. INTRODUCTION

With the continuously scaling of CMOS technology, the back-end-of-the-line (BEOL) interconnect wires are becoming narrower and closer to match the shrinking pitch of devices. Thus, parasitic capacitance and RC delay of interconnect wires increase dramatically and emerge as the limiting factor of circuit performance [1]-[2]. Simply yet physical capacitance models are highly preferred for analyzing and optimizing purpose.

Most of previous modeling work focused on the two dimensional (2D) cases. Models for three-dimensional (3D) structures are roughly estimated as C2D·L, and important capacitance components at wire ends are ignored. Thus, such approach often underestimates 3D wire capacitances, especially for those of short wires. The 2D modeling work can be categorized as either physical or empirical, i.e., fitting based solutions. The physical solutions tend to be either complex [3] or overly simplified so that some critical components are missing [4]-[6]. The empirical solutions give relatively accurate results, but they are tailored for specific structures and limited dimensions [7]-[8]. For more complicated structures such as the 3D cases, pure empirical fitting is quite complex and difficult to obtain accurate results for a wider range of dimensions [9]-[10].

Our previous effort successfully solved above issues by dividing electric field into different regions and solved the capacitance of each region separately [11]. In this work, the cases of 3D single line above an infinite plate and 3D parallel lines are considered following the same philosophy of dividing and conquering. Through the region partitions, the capacitance of every region is studied conveniently, and partitions ensure that the model has a solid physical foundation.

#### II. MODELING PRINCIPLES AND CASE STUDY

The most common BEOL structures include: 1) single line above a plate; 2) parallel lines. Compact models for these structures are foundations for the subsequent modeling of more complicated 3D interconnect structures.

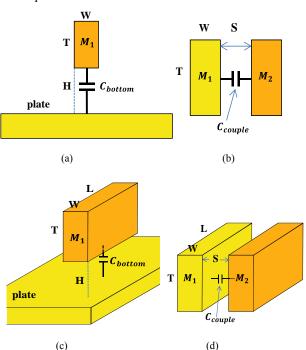

Fig.1 Common 2D and 3D BEOL structures.

<sup>&</sup>lt;sup>1</sup> Peking University Shenzhen SOC Key Laboratory, PKU HKUST Shenzhen-Hong Kong Institution, Shenzhen, China

<sup>&</sup>lt;sup>2</sup> School of Electronic Information Engineering Beijing University of Aeronautics and Astronautics, Beijing, China

<sup>&</sup>lt;sup>3</sup> Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Hong Kong

| Symbol                       | Capacitance Definitions                  |  |  |

|------------------------------|------------------------------------------|--|--|

| $C_{bottom}$                 | Wire to plate capacitance                |  |  |

| C <sub>couple</sub>          | Coupling capacitance between parallel    |  |  |

|                              | lines                                    |  |  |

| $C_{fringe}$                 | Capacitance of the fringe electric field |  |  |

| C <sub>terminal</sub>        | Capacitance of the terminal electric     |  |  |

|                              | field                                    |  |  |

| C <sub>terminal fringe</sub> | Capacitance of the terminal fringe       |  |  |

|                              | electric field                           |  |  |

| C <sub>3D terminal</sub>     | Capacitance of the 3D corner electric    |  |  |

|                              | field                                    |  |  |

Table 1: Definition of capacitances

As Fig.1 shows, Cbottom is the capacitance between a wire and an infinite plate, and Ccouple is the coupling capacitance between neighboring lines. Some commonly used dimensions are also labeled in Fig.1. Capacitances and their components are defined in Table I.

#### A. 2D model review

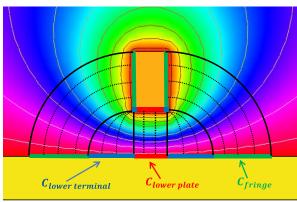

In [11], the 2D electric field between the wire and the infinite plate is divided into different regions as shown in Fig.2(a). Compact capacitance models are developed for each region. According to the Gaussian law, capacitance calculation can be simplified as (1) as long as electric field stays constant as it goes from one plate to the other plate.

$$dC = \frac{dQ}{V} = \frac{e \ d\Phi}{\int E \cdot d(distance)} = \frac{e \ d(area)}{distance}$$

(1)

Fig.2 (b) and (c) shows the shape of the electrical field of fringe capacitance and terminal capacitance respectively.

(a)

Fig.2 (a) Equal electric potential contours and the corresponding electrical field distribution. (b) Fringe capacitance. (c) Lower terminal camber capacitor with a radius of r.

The same as the plate capacitances, the magnitude of the electrical field of fringe capacitance does not change with distance. As a result, the 2D fringe capacitance can be derived accurately using

$$\frac{C}{c} = \int \frac{\text{width}}{\text{distance}}$$

(2)

On the other hand, the electric field will increase as it gets closer to the terminal of the wire in the terminal region. Thus, deriving terminal capacitance based on (2) will overestimate its value when H is large [11]. And pure physical solution leads to complicated results. For simplicity, semi-empirical models for lower and upper terminal capacitance are given as

$$\frac{c_{\text{lower terminal}}}{\varepsilon} = 1.3 \left(\frac{r}{H}\right)^{\beta}$$

(3a)

$$\frac{C_{\text{upper terminal}}}{\varepsilon} = 0.63 \left(\frac{r}{H + T}\right)^{\beta}$$

, (2b)

where r is the camber radius, mainly determined by H and positively correlated to W, T, and H. Based on simulation results, r and  $\beta$  are estimated as 0.09W0.2H0.5T0.2 and 0.25, respectively. All the other components are left unchanged from [11]. The total capacitance Cbottom is the summation of all the components.

Due to the COMSOL simulations [12], the rectified new model has smaller error over a wide range of dimensions compared to the previous models in general [4]-[8]. It is also generalized that as H increases, the terminal capacitance becomes dominant in the total capacitance.

3D modeling principles and capacitance formulas

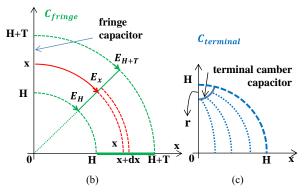

In this work, 3D capacitance models are developed using the same principle, the electric field is assigned into five major regions as illustrated in Fig.3. The partition is verified by simulations. The first three regions are natural extensions of the 2D cases and the last two regions are unique in the 3D cases.

- 1) Plate capacitance

- 2) Fringe capacitance

- 3) Terminal capacitance

- 4) 3D terminal capacitance: the electric field from the terminal of two sidewalls and the bottom plate to the ground plate.

- 5) Terminal fringe capacitance: the electric field from the perpendicular terminal line between two sidewalls to the ground plate.

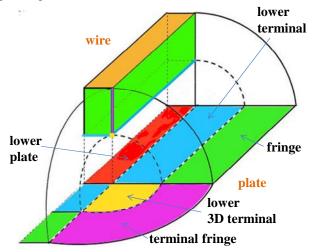

Fig.3 Distribution of electrical fields for a 3D single line above a plate.

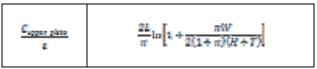

| Component                      | Model                                                          |  |  |

|--------------------------------|----------------------------------------------------------------|--|--|

| C <sub>ibrose</sub> gists<br>C | <u> 1872                                   </u>                |  |  |

| € <sub>trings</sub>            | $\frac{4(W+L)}{\pi}\ln\Bigl(1+\frac{T}{H}\Bigr)$               |  |  |

| Change to miles!               | $1.8(\frac{T_0}{H})^2W + 1.8\left(\frac{T_0}{H}\right)^2L$     |  |  |

| Cupper teminal                 | $0.68(\frac{T+T}{T_0})^{2}W + 0.68(\frac{T+T}{T_0})^{2}\Delta$ |  |  |

| Chose 20 teninal               | 10 v - em                                                      |  |  |

| Cupper 40 teninal              | ई ह - चत्रकर                                                   |  |  |

| Cisminal frings                | 277<br>In tan(0.50)                                            |  |  |

Table 2: Compact models of 3D single line above a plate where  $r_2$ = 0.09 $L^{0.2}H^{0.5}T^{0.2}$ ,  $r_2$ = 0.09 $W^{0.2}H^{0.5}T^{0.2}$ , r=( $r_1r_2$ )<sup>1/2</sup>,  $\beta$  = 0.25, and  $\delta$  = r/(H+0.4T).

The 3D plate capacitance, fringe capacitance and terminal capacitance can be simply calculated by multiplying 2D model with the corresponding length. For the 3D terminal components, semi-empirical formulas are given to avoid complex physical solutions. A simple physical solution for the terminal fringe capacitance is derived following the Gaussian Law. All the formulas are listed in Table II.

Finally by combining all the components, a 3D capacitance model for a single line above an infinite plate

(b) Fig.4 Verification of the single 3D line-to-plate capacitance

T [nm]

is completed as

0.000

10

$$\frac{c_{\text{bottom}}}{\varepsilon} = \frac{c_{\text{lower plate}}}{\varepsilon} + \frac{c_{\text{fringe}}}{\varepsilon} + \frac{2c_{\text{terminal}}}{\varepsilon} + \frac{c_{\text{upper plate}}}{\varepsilon} + \frac{c_{\text{terminal fringe}}}{\varepsilon} + \frac{c_{\text{1D terminal}}}{\varepsilon}. (4)$$

Using the method of image charge, after reducing the total

capacitance by half and replacing the following dimensions W = T, T = W,  $H = S/2 \rightarrow T$

the same equations can be used to calculate coupling capacitance of parallel lines.

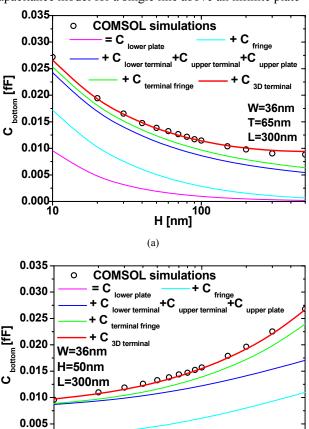

#### B. Validation of the 3D Line-to-Plate Capacitance

The nominal dimensions T=65nm, W=36nm, H=50nm from the ITRS latest updates [1], and a wire length of 300nm are used to verify the model in Fig.4. The new model well matches COMSOL simulation results. The physical nature of the model guarantees scalability with all the wire dimensions. As Fig.4 shows, the most important part in the total capacitance is again the terminal component, not the widely known plate capacitance. The terminal fringe and 3D terminal capacitance, which are usually ignored, are also important, especially when L is short.

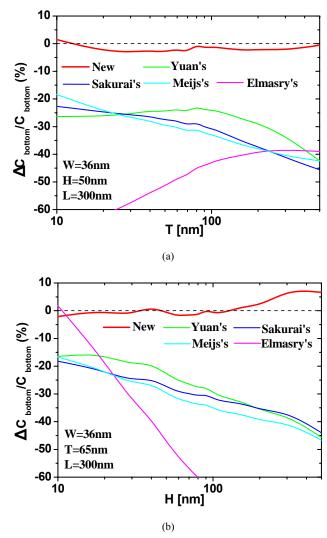

# III. 3D MODEL COMPARISON AND DISCUSSION

For the 3D structure, Table III evaluates the model accuracy at different dimension corners. The error is well below 5% for all cases. Fig.5 compares the new 3D model with C2D·L from the previous methods [4]-[8]. The new 3D model captures the important 3D components and has excellent accuracy compared to other models, even when wire length is large.

| Dimensions(nm)    | C <sub>bottom</sub> (fF) |            |          |

|-------------------|--------------------------|------------|----------|

| {W,T,H,L}         | Model                    | Simulation | Error(%) |

| {36,65,50,300}    | 0.0138                   | 0.0141     | -2.2572  |

| {36,65,50,10000}  | 0.3454                   | 0.3454     | 0.0011   |

| {36,65,100,300}   | 0.0114                   | 0.0116     | -1.6762  |

| {36,65,100,10000} | 0.2637                   | 0.2553     | 3.3160   |

| {36,100,50,300}   | 0.0155                   | 0.0157     | -1.3523  |

| {36,100,100,300}  | 0.0129                   | 0.0130     | -0.4700  |

| {1000,65,50,300}  | 0.0998                   | 0.0992     | -0.6612  |

| {1000,65,100,300} | 0.0666                   | 0.0655     | 1.5892   |

| {1000,100,50,300} | 0.1047                   | 0.1027     | 2.0052   |

Table 3: Comparison of the model with comsol aimulation

Fig.5 3D model error compared with some previous results

### IV. CONCLUSION

This paper has presented a physical electric field based model of the bottom and coupling capacitance for the basic cases of the interconnect wires. Different from previous approaches, the new models for 2D and 3D structures are given by an in-depth analysis of the electric field distribution. The terminal fringe capacitance and 3D terminal capacitance have been identified as important components in 3D cases, and become more and more significant as the length of the wire shrinks. The models have been validated by the numerical solutions.

#### ACKNOWLEDGMENT

This work is supported by the Key Project of National natural Science Funds of China (60936005), the Shenzhen Science & Technology Foundation (CXB201005250031A), the Fundamental Research Project of Shenzhen Science & Technology Foundation (JC201005280670A), the International Collaboration Project of Shenzhen Science & Technology Foundation (ZYA2010006030006A).

# REFERENCES

- [1] The International Technology Roadmap for Semiconductor (ITRS), 2010.

- [2] A. Jarosz, "Neighbourhood problem in interconnection capacitance modeling", TCSET 2002, February 18-23,2002, Lviv Slavsko, Ukraine.

- [3] W. H. Chang,, "Analytic IC-metal-line capacitance formulas," IEEE Trans. Microw. Theory Tech., vol. MTT-24, no. 9, pp. 608–611, Sep. 1976.

- [4] M. I. Elmasry, "Capacitance calculation in MOSFET VLSI," IEEE Electron Device Lett., vol. EDL-3, no. 1, pp. 6–7, Jan. 1982.

- [5] C. P. Yuan and T. N. Trick, "A simple formula for the estimation of the capacitance of two-dimensional interconnects in VLSI circuit," IEEE Electron Device Lett., vol. EDL-3, no. 12, pp. 391–393, Dec. 1982.

- [6] E. Barke, "Line-to-ground capacitance calculation for VLSI: A comparison," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.,vol.7, no. 2, pp. 295–298, Feb. 1988.

- [7] N. van der Meijs and J. T. Fokkema, "VLSI circuit reconstruction from mask topology," Integr. VLSI J., vol. 2, no. 2, pp. 85–119, Jun. 1984.

- [8] T. Sakurai and K. Tamaru, "Simple formulas for two- and three-dimensional capacitances," IEEE Trans. Electron Devices, vol. ED-30, no. 2, pp. 183–185, Feb. 1983.

- [9] S.-C. Wong, G.-Y. Lee, and D.-J. Ma, "Modeling of interconnect capacitance, delay, and crosstalk in VLSI," IEEE Trans. Semicond. Manuf.,vol. 13, no. 1, pp. 108–111, Feb. 2000.

- [10] S.-C. Wong, T. G.-Y. Lee, D.-J. Ma, and C.-J. Chao, "An empirical three-dimensional crossover capacitance model for multilevel interconnect VLSI circuits," IEEE Trans. Semicond. Manuf., vol. 13, no. 2, pp. 219–227, May 2000.

- [11] Wei Zhao, Xia Li, Sam Gu, Seung H. Kang, Matthew M. NNowak and Yu Cao, "Field-based capacitance modeling for sub-65-nm on-chip interconnect", IEEE Transactions on Electron Devices, vol. 56, no. 9, September 2009.

- [12] COMSOL Multi-Physics User's Manual. [Online]. Available: www.comsol.com/products.