# **Electrical Characteristics of 16-nm Multi-Gate-and-Multi-Fin Field Effect Transistors and Digital Circuits**

Hui-Wen Cheng<sup>1</sup> and Yiming Li<sup>1,2,\*</sup>

<sup>1</sup>Department of Electrical Engineering and Institute of Communications Engineering, National Chiao Tung University, Hsinchu 300, Taiwan; <sup>2</sup>National Nano Device Laboratories, Hsinchu 300, Taiwan \*ymli@faculty.nctu.edu.tw

### **ABSTRACT**

The structure with vertical channel is attractive due to suppression of the short-channel effect, where the shape of silicon fin determines the device performance. In this work, the DC characteristics of single-fin FinFET are simulated, which shows a better immunity against fluctuation induced by random dopant than that of tri-gate and quasi-planar fin shapes. Increasing the number of silicon fins of FinFET can further improve the performance. Examining the fluctuation induced by random dopant in CMOS inverter and SRAM circuits with triple-fin structure shows that the fluctuation of intrinsic gate delay and SNM in triple-fin FinFET are smaller and larger, respectively, than that of others due to higher driving current.

*Keywords*: Fin aspect ratio, FinFET, Tri-gate FET, Coplanar FET, Static noise margin, Gate delay, Random-dopant-induced fluctuations, 3D density-gradient equations

## 1 INTRODUCTION

As the gate length of bulk metal oxide semiconductor field effect transistor (MOSFET) shrinks below 32 nm, devices with vertical channel have drawn people's attention due to diverse fascinating characteristics [1-3]. Multi-gate-and-multi-fin FETs have thus been proposed to provide a large driving capability [3]. Investigation of DC and AC characteristics of multi-gate-and-multi-fin devices plays a crucial role for IC application; unfortunately, studies on their digital circuits' behavior and random-dopant-induced fluctuations have not been clearly drawn yet.

In this work, we estimate electrical characteristics including threshold voltage  $(V_{th})$  and gate capacitance  $(C_g)$  of 16-nm-gate multi-gate-and-multi-fin FETs, and delay time of an inverter and static noise margin (SNM) of a 6T SRAM. Large-scale random-dopant-induced fluctuations of the aforementioned characteristics are further discussed with respect to different fin aspect ratio (AR = the fin height / the effective fin width), where the device characteristics are obtained by solving a set of 3D density-gradient equations coupled with Poisson equations as well as electron-hole current continuity equations [3] under our parallel computing system [4]. Notably, an experimentally validated simulation [5] is also conducted to investigate the fluctuation property.

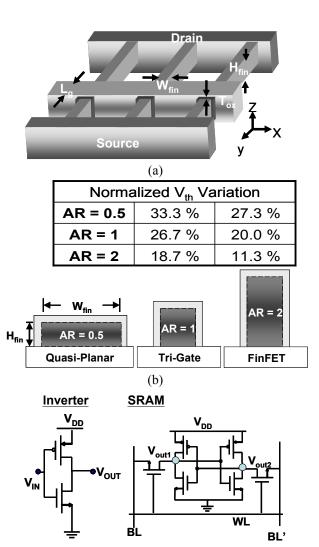

Figure 1: (a) A schematic and (b) fin cross-section view of triple-fin MOSFET. The fin shapes of transistor are FinFET (AR = 2), tri-gate (AR = 1) and quasi-planar (AR = 0.5) and their normalized  $V_{th}$  variation are summarized in the table, where the normalized  $V_{th}$  variation is defined as the difference of  $V_{th}$  between the 14.5-nm- and the 17.5-nm-gate lengths divided by the nominal  $V_{th}$ . (c) Inverter and SRAM are used as the test circuit, where  $V_{DD}$  is 1  $V_{\cdot}$

(c)

#### 2 SIMULATION TECHNOLOGY

The nominal channel doping concentration of the explored devices is 1.48 x 10<sup>18</sup> cm<sup>-3</sup>. They have a 16 nm gate, a gate oxide thickness of 1.2 nm, and a work function of 4.4 eV. Considering the effect of random dopant fluctuation (RDF), we take FinFET shape as a generation example of random dopant. There are 378 dopants are first randomly generated in a cube of 80 x 40 x 80 (nm)<sup>3</sup>. The 80 x 40 x 80 (nm)<sup>3</sup> cube is then partitioned into 125 subcubes of 16 x 8 x 16 (nm)<sup>3</sup>. The number of dopants in each subcube varies from zero to 9, with an average of three. The 125 generated subcubes are then equivalently mapped into the channel region of the device channel for the 3D device simulations with discrete dopants.

The device simulation is performed by solving a set of 3D density-gradient equations coupled with Poisson equations as well as electron-hole current continuity equations [6-9] on a parallel computing system [10-16]. In "atomistic" device simulation, the resolution of individual charges within a conventional drift-diffusion simulation using a fine mesh creates problems associated with singularities in the Coulomb potential [17]. The potential becomes too steep with fine mesh, and therefore, the majority carriers are unphysically trapped by ionized impurities, and the mobile carrier density is reduced. Thus, the density-gradient approximation is used to handle discrete charges by properly introducing related quantummechanical effects, and coupled with Poisson equation as well as electron-hole current continuity equations [18-19]. The accuracy of the simulation technique was confirmed by comparing simulated fluctuation results with measurements of experimentally fabricated 20 nm devices.

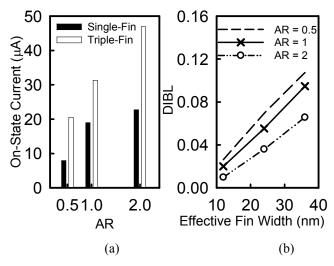

Figure 2: (a) Plots of the on-state current for the 16-nm-gate single-fin and triple-fin MOSFETs with AR = 0.5, 1 and 2. (b) DIBL for 16-nm-gate triple-fin MOSFETs with AR = 0.5, 1 and 2.

#### 3 RESULTS DISCUSSION

Figure 1(a) illustrates the studied 3D triple-fin transistors. The Fig. 1(b) shows the plot of fin cross-section views for FinFETs (AR = 2), tri-gate (AR = 1) and quasiplanar (AR = 0.5), respectively. The inset table of Fig. 1(b) presents that the normalized V<sub>th</sub> of triple-fin FinFET is 1.7 (18.7 / 11.3 = 1.7) times smaller than single-fin FinFET transistors that means the short channel effect can be suppressed well. To compare the device characteristics on a fair basis, the cross-section area of the fin for the explored devices are fixed at about 128 nm<sup>2</sup>. The similar crosssection area and V<sub>th</sub> indicates the same control volume of device channel under the same operation condition. Figure 1(c) shows the inverter and SRAM circuits which are tested for electrical characteristics of multi-fin device. The device gate length is chosen as 16 nm. The V<sub>th</sub> of the explored 16nm-gate transistors are calibrated to 150 mV.

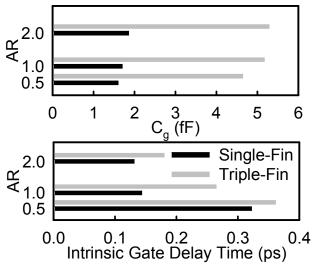

Figure 3: The upper and lower plot show the gate capacitance and intrinsic gate delay time for the 16-nm-gate single-fin and triple-fin MOSFETs with different fin structure, respectively.

The on-state current of triple-fin FinFET has larger onstate current than single-fin FinFET, as shown in Fig. 2(a). Comparison of different fin shape shows that the DIBL of triple-fin FinFET is 1.63 times smaller than quasi-planar MOSFET due to better gate control capability, where the effective fin width is the sum of the fin width and two times fin height. The upper illustration of Fig. 3 demonstrates the gate capacitance of the 16-nm-gate single- and triple-fin devices. Compared with the triple-fin quasi-planar devices,  $C_g$  of triple-fin FinFETs is increased by a factor of 3.7. The large  $C_g$  of triple-fin MOSFET with a large AR enhances charge control; nevertheless, the increased  $C_g$  affects the operation speed of transistors. In order to study the trade-off

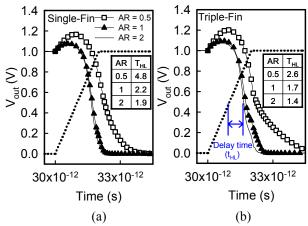

Figure 4: The high-to-low transition for (a) single-fin and (b) triple-fin MOSFET with AR = 0.5, 1 and 2, where the high-to-low delay time is defined in the inset.

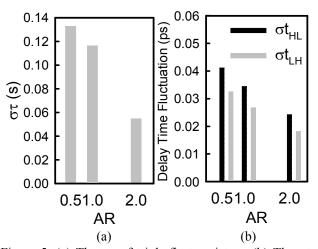

Figure 5: (a) The  $\sigma\tau$  of triple-fin transistors. (b) The  $\sigma t_{HL}$  and  $\sigma t_{LH}$  of the tested inverter with AR = 0.5, 1 and 2, respectively.

between I<sub>on</sub> and C<sub>g</sub>, we calculate intrinsic gate delay of transistor ( $\tau = C_g V_{DD}$  /  $I_{on}$ ), as shown in the lower illustration of Fig. 3. The results show that single-fin FinFET presents 1.1 and 2.5 times smaller than that of the tri-gate FinFET and the quasi-planar MOSFET due to relatively smaller C<sub>g</sub>. Then we test the performance of single- and multi-fin MOSFET in inverter circuit, as shown in Fig. 4. As expected, both single- and triple-fin FinFET inverters present smallest t<sub>HL</sub> with respect to different AR and show the benefit of FinFET in both DC and dynamic characteristics. Although the gate capacitance of the triplefin transistor is larger, it provides a smaller transition delay than that of the single-fin transistor due to increase of driving current. Consider the fluctuations induced by random-dopant, the  $\sigma\tau$  of triple-fin FinFET is 2.4 times smaller than that of single-fin one. Though C<sub>g</sub> of triple-fin

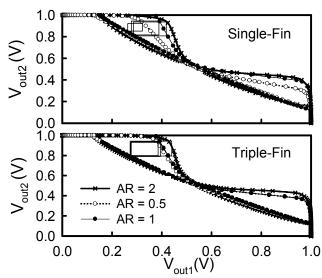

Figure 6: The upper and lower plot of static transfer characteristics for single- and multi-fin with AR = 0.5, 1 and 2, respectively.

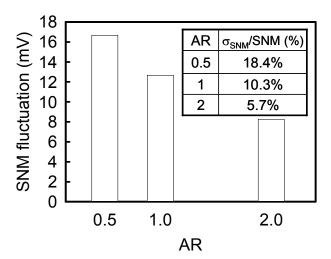

Figure 7: SNM fluctuation of the examined multi-fin structure with AR = 0.5, 1 and 2, respectively. The normalized  $\sigma$ SNM is summarized in the inset table.

FinFETs is quite large, the large on-state current reduces the στ of triple-fin FinFET, as shown in Fig. 5(a). Fig. 5(b) shows the delay time of triple-fin FinFET inverter has 2.4 times smaller than triple-fin quasi-planar MOSFET because of better driving capability. And the σt<sub>HL</sub> exceeds σt<sub>LH</sub> due to controlled by n-FETs which has larger mobility. For SRAM examination, the static transfer characteristic of triple-fin transistor shows larger SNM than single-fin transistor, as shown in Fig. 6. The triple-fin FinFET exhibits the largest SNM among the explored three structures, where the SNM is calculated from the length of the side of a square having the longest diagonal. The cell ratio and pull-up ratio are assumed to be one in this examination. Fig. 7 presents the random-dopant-induced

SNM fluctuation ( $\sigma$ SNM) of the triple-fin devices SRAM cells and the triple-fin FinFETs has the smallest  $\sigma$ SNM due to smallest normalized  $V_{th}$ , where the normalized  $\sigma$ SNM are summarized in the inset table of Fig. 7.

#### 4 CONCLUSIONS

The DC characteristics and dynamic behavior of 16-nm-gate multi-gate-and-multi-fin devices and circuits with different AR have been examined including random-dopant-induced fluctuations. Increase of the fin number and AR is revealed to be favorable for device performance with a view to suppression of SCE and relatively moderate enhancement in current drive. The triple-fin FinFET has exhibited a promising SCE, driving current, timing characteristic, SNM, and fluctuation resistivity than the triple-fin tri-gate and the quasi-planar MOSFET. We are currently studying the optimal fin number and pinch distance among channel fins for the manufacturability of multi-fin FinFETs. In addition, parasitic capacitances of these devices are crucial for advanced multi-gate-and-multi-fin transistor design.

#### **ACKNOWLEDGEMENT**

This work was supported in part by Taiwan National Science Council (NSC) under Contract NSC-97-2221-E-009-154-MY2 and by TSMC, Taiwan, under a 2008-2010 grant.

#### REFERENCES

- [1] J. P. Colinge, (Ed.) FinFETs and Other Multi-Gate Transistors, Springer, 2007.

- [2] Y. Li and C.-H. Hwang, "Effect of Fin Angle on Electrical Characteristics of Nanoscale Round-Top-Gate Bulk FinFETs," IEEE Trans. Electron Devices, pp. 3426-3429, 2007.

- [3] H.-W. Cheng, C.-H. Hwang and Y. Li, "Impact of Channel Fin Aspect Ratio on Multi-Fin Field Effect Transistors," Int. J. Elec. Eng., vol. 16, pp. 301-311, 2009.

- [4] Y. Li and S.-M. Yu, "A Parallel Adaptive Finite Volume Method for Nanoscale Double-gate MOSFETs Simulation," J. Comput. Appl. Math., vol. 175, pp. 87-99, 2005.

- [5] Y. Li S.-M. Yu, J.-R. Hwang, F.-L. Yang, "Discrete dopant fluctuated 20 nm/l5 nm-gate planar CMOS," IEEE Trans. Electron Devices, vol. 55 pp. 1449-1455, 2008.

- [6] M. G. Ancona and H. F. Tiersten, "Macroscopic Physics of the Silicon Inversion Layer" Phys. Rev. B vol. 35, pp. 7959-7965, 1987.

- [7] S. Odanaka, "Multidimensional discretization of the stationary quantum drift-diffusion model for ultrasmall MOSFET structures," IEEE Trans.

- Comput. Aided Des. Integr. Circuits Syst., vol 23, pp. 837-842, 2004.

- [8] T.-W. Tang, X. Wang, and Y. Li, "Discretization Scheme for the Density-Gradient Equations and Effect of Boundary Conditions," J. Comput. Electron., vol. 1, pp. 389-393, 2002.

- [9] G. Roy, A. R. Brown, A. Asenov, and S. Roy, "Quantum aspects of resolving discrete charges in atomistic device simulation," J. Comput. Electron., vol. 2, pp. 323-327, 2003.

- [10] Y. Li and S.-M. Yu, "Comparison of Random-Dopant-Induced Threshold Voltage Fluctuation in Nanoscale Single-, Double-, and Surrounding-Gate Field-Effect Transistors" Jpn. J. Appl. Phys., vol. 45, pp. 6860-6865, 2006.

- [11] Y. Li, S.-M. Yu, J.-R. Hwang, and F.-L. Yang, "Discrete dopant fluctuated 20 nm/l5 nm-gate planar CMOS," IEEE Trans. Electron Devices, vol. 55, pp. 1449-1455, 2008.

- [12] F.-L. Yang, J.-R. Hwang, and Y. Li, "Electrical Characteristic Fluctuations in Sub-45nm CMOS Devices," IEEE Custom Integrated Circuits Conf., pp. 691-694, 2006.

- [13] Y. Li, S.-M. Yu and H.-M. Chen, "Process-variation- and random-dopants-induced threshold voltage fluctuations in nanoscale CMOS and SOI devices," Microelectron. Eng., vol. 84, pp. 2117-2120, 2007.

- [14] Y. Li, C.-H Hwang and H.-W. Cheng, "Discrete-Dopant-Fluctuated Transient Behavior and Variability Suppression in 16-nm-Gate Complementary Metal-Oxide-Semiconductor Field Effect Transistors," Jpn. J. Appl. Phys., vol. 48, 04C051, 2009.

- [15] Y. Li and S.-M. Yu, "A parallel adaptive finite volume method for nanoscale double-gate MOSFETs simulation," J. Comput. Appl. Math., vol. 175, pp. 87-99, 2005.

- [16] Y. Li, H.-M. Lu, T.-W. Tang, and S. M. Sze, "A novel parallel adaptive Monte Carlo method for nonlinear Poisson equation in semiconductor devices," Math. Comput. Simulation, vol. 62, pp. 413-420, 2003.

- [17] Y. Li, C.-H Hwang and H.-W. Cheng, "Process-Variation- and Random-Dopants-Induced Threshold Voltage Fluctuations in Nanoscale Planar MOSFET and Bulk FinFET Devices," Microelectronic Engineering," Microelectron. Eng., vol. 86, pp. 277-282, 2009.

- [18] B. Cheng, S. Roy, G. Roy, A. Brown, and A. Asenov: Proc. 36th Eur. Solid-State Device Research Conf., pp. 258-261, 2006.

- [19] H. Mahmoodi, S. Mukhopadhyay, and K. Roy, "Estimation of delay variations due to randomdopant fluctuations in nanoscale CMOS circuits," IEEE Journal of Solid-State Circuits," IEEE J. Solid-State Circuits, vol. 40, pp. 1787-1796, 2005.