# Comprehensive Examination of Intrinsic-Parameter-Induced Characteristic Fluctuations in 16-nm-Gate CMOS Devices

Ming-Hung Han<sup>1</sup>, Yiming Li<sup>1,2,\*</sup>, Kuo-Fu Lee<sup>1</sup>, Hui-Wen Cheng<sup>1</sup>, and Zhong-Cheng Su<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering and Institute of Communications Engineering, National Chiao Tung University, Hsinchu 300, Taiwan; <sup>2</sup>National Nano Device Laboratories, Hsinchu 300, Taiwan \*Email: ymli@faculty.nctu.edu.tw

# **ABSTRACT**

Intrinsic parameter fluctuations on device characteristic and yield are crucial in determining the operation of nanoscale semiconductor devices. In this paper, we examine the fluctuations of the threshold voltage (V<sub>th</sub>), gate capacitance (Cg), and cutoff frequency (FT) of emerging metal/high-κ gate planar complementary metal-oxidesemiconductor (CMOS) field effect transistors (FETs) variability including metal-gate-workfunction fluctuation (WKF), random-dopant fluctuation (RDF), and processvariation effect (PVE). An experimentally validated 3D "atomistic" simulation allows us to investigate the effect of aforementioned fluctuation sources on device DC/AC property. The preliminary results show that RDF and WKF dominate the device DC characteristics for n-type MOSFET (NMOS) and p-type MOSFET (PMOS), respectively. PVE affects CMOS device AC characteristics, especially at high gate bias.

*Keywords*: MOSFET, Characteristic fluctuation; Random-dopant fluctuation; Process-variation effect; Work-function fluctuation; Modeling and simulation

# 1 INTRODUCTION

The size of complementary metal-oxide-semiconductor (CMOS) field effect transistors (FETs) have been rapidly scaled down and the variability become a major challenge to device technologies. For state-of-art nanoscale CMOS circuits and systems, the intrinsic device parameter fluctuations that result from line-edge roughness, the granularity of the polysilicon gate, random discrete dopants [1-16], and other causes have substantially affected signal system timing [16] and high-frequency characteristics [15]. Yield analysis and power reduction, which take into account the manufacturing tolerances, model uncertainties, variations in the process parameters, and so forth, are known as indispensable components of circuit design. Diverse approaches have recently been presented to investigate and suppress the intrinsic-parameter fluctuations in semiconductor devices [4,5,14-16]. Among these approaches, the high-κ/metal-gate technology is the key to reduce the intrinsic-parameter fluctuations. However, the use of metal as a gate material introduces a new source of random variation due to the dependence of work function on the orientation of metal grains [17-20]. The change of CMOS device characteristics, caused by intrinsic device parameter variations, increased as the size is reduced; it may result in failure of integrated circuits with such small CMOS devices. Therefore, it is urgent to examine the intrinsic-parameter-induced CMOS device characteristic fluctuations.

In this work, organized as follow, we first propose the simulation methodology of intrinsic device parameter variability including the metal gate workfunction fluctuation (WKF), the process variation effect (PVE), and the random dopant fluctuation (RDF). Then we comprehensively investigate the intrinsic parameter variability induced threshold voltage ( $V_{th}$ ), gate capacitance ( $C_g$ ), and cutoff frequency ( $F_T$ ) of fluctuations on 16-nm metal/high- $\kappa$  gate n-type MOSFETs (NMOS) and p-type MOSFETs (PMOS). The results of this study show that RDF dominates the NMOS device characteristics, and WKF is major factor in PMOS. PVE affect the CMOS device AC characteristics, especially at high gate bias.

# 2 SIMULATION METHODOLOGY

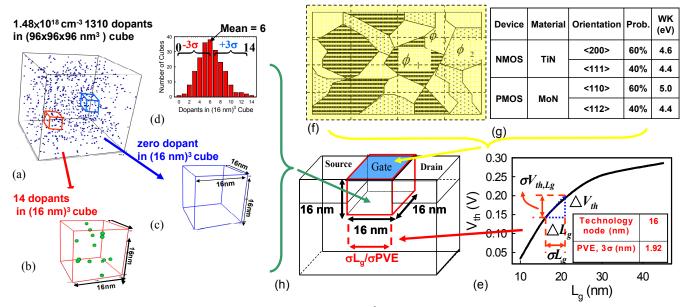

The explored devices are the 16-nm-gate CMOS devices (width: 16 nm) with amorphous-based TiN / HfSiON gate stacks and an EOT of 1.2 nm. The nominal channel doping concentrations are 1.48x10<sup>18</sup> cm<sup>-3</sup> and the threshold voltage are 140 mV. To fairly compare the characteristic fluctuations and eliminate effects of the transistor size on the fluctuation, the same dimension, channel doping, and V<sub>th</sub> are assumed for the 16-nm-gate NMOS and PMOS devices. Figures 1(a)-1(d) illustrate the RDF-induced fluctuation, the simulation mainly follows our recent work [9-17], in which 1310 dopants are randomly generated in a large cube of (96 nm)<sup>3</sup>, in which the equivalent doping concentration is 1.48x10<sup>18</sup> cm<sup>-3</sup>. Then the large cube is partitioned into 216 sub-cubes of (16 nm)<sup>3</sup> and mapped into the device channel for the three dimensional (3D) device simulations with discrete dopants, as shown in Fig. 1(h). Notably, the maximum and minimum  $V_{th}$  are achieved for this specific set of 216 randomized channels would be different (larger range) if a larger number of samples were taken. Note that, comparing with a simulation of 1000 discrete dopant devices, the difference of the obtained

Figure 1: (a) 1310 dopants are randomly generated in a (96 nm)<sup>3</sup> cube, in which the equivalent doping concentration is 1.48×10<sup>18</sup> cm<sup>-3</sup>. The large cube is then partitioned into 216 (16nm)<sup>3</sup> sub-cubes ((b)-(d)). (e) The magnitude of PVE follows the ITRS to estimate the PVE induced device fluctuations. (f) The gate area is composed of a small number of grains, and the estimation of WKF according to the metal properties in (g). (h) The explored 16 nm planar MOSFETs for 3D simulation.

threshold voltage fluctuation ( $\sigma V_{th}$ ) for the set of fluctuation sources of device characteristics variations are 216 randomized devices is only 1 mV. Therefore, the major fluctuation sources are the same. The PVE in this work include the gate length deviation and line edge roughness. We assume the magnitudes of PVE are Gaussian distribution and follow the projection of ITRS [22], as shown in Fig. 1(e). For WKF in Fig. 1(f), a Monte-Carlo approach is proposed for examining such effect, the gate area is first partitioned into several parts. Then, the workfunction of each partitioned area is randomized following the properties of metal in Fig. 1(g) [18, 19]. The effective workfunction of single device is the average of all partitions and uses for estimation of WKF-induced characteristics fluctuations. There are 200 devices generated for PVE and WKF, respectively. The physical model and accuracy of simulation approach have been quantitatively calibrated experimentally measured results [10].

# 3 RESULTS AND DISCUSSION

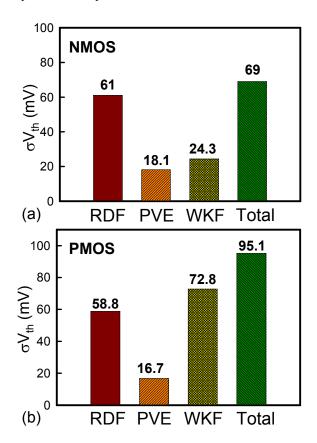

Figures 2(a) and 2(b) show  $\sigma V_{th}$  for NMOS and PMOS, respectively. The total  $V_{th}$  fluctuation,  $\sigma V_{th,total}$ , according to the independency of the fluctuation components, is given below,

$$\sigma_{V_{th,total}}^{2} = \sigma_{V_{th,RDF}}^{2} + \sigma_{V_{th,PVE}}^{2} + \sigma_{V_{th,WKF}}^{2}, \qquad (1)$$

where  $\sigma V_{th,PVE}$ ,  $\sigma V_{th,WKF}$ , and  $\sigma V_{th,RDF}$ , are the RDF-, PVE-, and WKF-induced  $V_{th}$  fluctuations. From simulation results,

Figure 2: The threshold voltage fluctuations induced by intrinsic parameter variations for the 16 nm (a) n-type and (b) p-type planar MOSFETs.

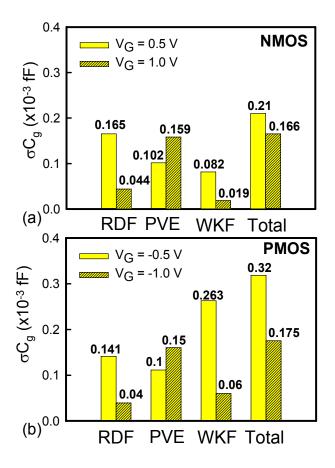

Figure 3: The gate capacitance fluctuations induced by intrinsic parameter variations for the 16 nm (a) n-type and (b) p-type planar MOSFETs.

the random-dopant fluctuation dominates the fluctuation of  $V_{th}$  in NMOS.However, for the fluctuation of  $V_{th}$  in PMOS, the workfunction fluctuation becomes the dominating factor because of the large deviation of the workfunction for different orientation of metal grains. The total threshold voltage fluctuations for NMOS and PMOS are 69 mV and 95 mV, respectively.

Figure 3 shows the gate capacitance fluctuations ( $\sigma C_g$ ) for NMOS and PMOS at  $V_G = 0.5V$  and 1V. Similarly, the total gate capacitance ( $C_g$ ) fluctuation,  $\sigma C_{g,total}$  is given,

$$\sigma_{C_{\sigma \text{ total}}}^2 = \sigma_{C_{\sigma \text{ RDF}}}^2 + \sigma_{C_{\sigma \text{ PVE}}}^2 + \sigma_{C_{\sigma \text{ WKF}}}^2, \qquad (2)$$

where  $\sigma V_{Cg,PVE}$ ,  $\sigma V_{Cg,WKF}$ , and  $\sigma V_{Cg,RDF}$ , are the RDF-, PVE-, and WKF-induced  $C_g$  fluctuations. The results are similar to the results of  $\sigma V_{th}$  at low gate bias ( $V_G = 0.5V$ ), RDF and WKF are dominate variation sources. However, the RDF and WKF brought less impact on  $\sigma C_g$  due to the screening effect of the inversion layer at high gate bias ( $V_G = 1V$ ). The screening effect isolates the variation of surface electrostatic potential and decreases the  $\sigma C_g$ . The PVE gives

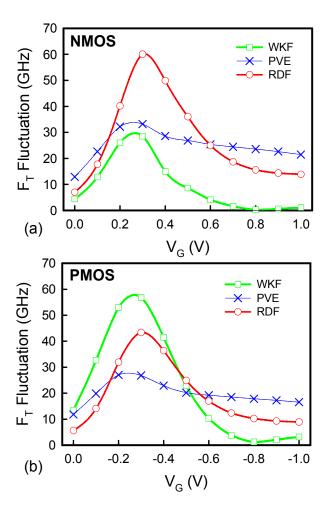

Figure 4: The cutoff frequency fluctuations induced by intrinsic parameter variations for the 16 nm (a) n-type and (b) p-type planar MOSFETs.

sizeable impact on the gate length and is independent of the screening effect, which should be noticed when the transistor operated at high gate bias.

Figures 4(a) and 4(b) illustrate the intrinsic parameter fluctuation induced cutoff frequency fluctuations ( $\sigma F_T$ ) as a function of gate voltage for NMOS and PMOS, respectively. The cutoff frequency ( $F_T$ ) is calculated as below:

$$F_T = v_{sat} / 2\pi L_g = g_m / 2\pi C_g.$$

(3)

The simulation results show that RDF and PVE are important in NMOS at low and high gate bias, and the impact of WKF can be neglected. In PMOS at low gate bias, besides the WKF, RDF is still also a major variation source, and PVE is important at high gate bias, which similar to the results of  $\sigma C_g$ . All the RDF, PVE, and WKF should be carefully considered in PMOS' AC characteristics.

## 4 CONCLUSIONS

In this paper, we have comprehensively explored the impact of intrinsic parameter fluctuations, WKF, PVE and RDF on DC and AC characteristics' fluctuation for 16-nmgate planar CMOS devices. By experimentally validated three dimensional atomistic simulation, RDF and WKF dominate the device DC characteristics for NMOS and PMOS, respectively. For AC characteristics, the RDF and PVE are important in NMOS at low and high gate bias, and the impact of WKF can be neglected. In PMOS at low gate bias, besides the WKF, RDF is still also a major variation source, and PVE is important at high gate bias. All the RDF, PVE, and WKF should be carefully considered in AC characteristics of PMOS.

### ACKNOWLEDGEMENT

This work was supported in part by Taiwan National Science Council (NSC) under Contract NSC-97-2221-E-009-154-MY2 and by TSMC, Taiwan, under a 2008-2010 grant.

### REFERENCES

- [1] H.-S. Wong, Y. Taur, and D. J. Frank, "Discrete Random Dopant Distribution Effects in Nanometer-Scale MOSFETs," Microelectronics Reliability, 38, 1447, 1999.

- [2] X.-H. Tang, V.K. De, and J.D. Meindl, "Intrinsic MOSFET Parameter Fluctuations Due to Random Dopant Placement," IEEE Trans. VLSI Systems, 5, 369, 1997.

- [3] P.A. Stolk, F.P. Widdershoven, and D.B.M. Klaassen, "Modeling statistical dopant fluctuations in MOS transistors," IEEE Trans. Electron Device, 45, 1960, 1998.

- [4] A. Asenov, S. Kaya, and A. R. Brown, "Intrinsic parameter fluctuations in decananometer MOSFETs introduced by gate line edge roughness," IEEE Trans. Electron Devices, 50, 1254, 2003.

- [5] G. Roy, A. R. Brown, F. Adamu-Lema, S. Roy, and A. Asenov, "Simulation study of individual and combined sources of intrinsic parameter fluctuations in conventional nano-MOSFETs," IEEE Trans. Electron Devices, 53, 3063, 2006.

- [6] J.Y. Chen, "GPU Technology Trends and Future Requirements," IEDM Tech. Dig., 1, 2009.

- [7] G. Tsutsui, M. Saitoh, T. Nagumo and T. Hiramoto, "Impact of SOI thickness fluctuation on threshold voltage variation in ultra-thin body SOI MOSFETs," IEEE Trans. Nanotechnology, 4, 363, 2005.

- [8] S. Xiong and J. Bokor, "A simulation study of gate line edge roughness effects on doping profiles of short-channel MOSFET devices," IEEE Trans. Elec. Dev., 51, 228, 2004.

- [9] Y. Li, and C.-H Hwang, "Discrete-dopant-induced characteristic fluctuations in 16 nm multiple-gate

- silicon-on-insulator devices", J. Appl. Phys. 102, 084509, 2007.

- [9] Y. Li, and S.-M. Yu, "A Coupled-Simulation-and-Optimization Approach to Nanodevice Fabrication With Minimization of Electrical Characteristics Fluctuation," IEEE Trans. Semi. Manufacturing, 20, 432, 2007.

- [10] F.-L. Yang, J.-R. Hwang, H.-M. Chen, J.-J. Shen, S.-M. Yu, Y. Li, and Denny D. Tang, "Discrete Dopant Fluctuated 20nm/15nm-Gate Planar CMOS," VLSI Tech. Symp. Dig., 208, 2007.

- [11] Y. Li, and C.-H Hwang, "Electrical characteristic fluctuations in 16nm bulk-FinFET devices", Microelectronics Engineering, 84, 2093, 2007.

- [12] F.-L. Yang, J.-R. Hwang, and Y. Li, "Electrical Characteristic Fluctuations in Sub-45nm CMOS Devices," Proc. IEEE Custom Integrated Circuits Conf., 691, 2006.

- [13] Y. Li and S.-M. Yu, "Comparison of Random-Dopant-Induced Threshold Voltage Fluctuation in Nanoscale Single-, Double-, and Surrounding-Gate Field-Effect Transistors," Jpn. J. Appl. Phys., 45, 6860, 2006.

- [14] Y. Li, and S.-M. Yu, "A study of threshold voltage fluctuations of nanoscale double gate metal-oxide-semiconductor field effect transistors using quantum correction simulation," J. Comp. Elect. 5, 125, 2006.

- [15] Y. Li and C.-H. Hwang, "High-frequency characteristic fluctuations of nano-MOSFET circuit induced by random dopants," IEEE Trans. Microw. Theory Tech., 56, 2726, 2008.

- [16] Y. Li C.-H. Hwang and T.-Y. Li, "Discrete-dopant-induced timing fluctuation and suppression in nanoscale CMOS Circuit," IEEE Trans. Microw. Theory Tech., 56, 2726, 2008.

- [17] H. Dadgour, Z. Endo, V. De, and K. Banerjee, "Modeling and analysis of grain-orientation effects in emerging metal-gate devices and implications for SRAM reliability," IEDM Tech. Dig., 1, 2008.

- [18] H. Dadgour, V. De, and K. Banerjee, "Statistical modeling of metal-gate work-function variability in emerging device technologies and implications for circuit design," ICCAD, 270, 2008.

- [19] K. Ohmori, T. Matsuki, D. Ishikawa, T. Morooka, Y. Sugita, T. Chikyow, K. Shiraishi, Y. Nara, and K. Yamada, "Impact of additional factors in threshold voltage variability of metal/high-κ gate stacks and its reduction by controlling crystalline structure and grain size in metal gates", IEDM Tech. Dig., 409, 2008.

- [20] T. Matsukawa, S. Ouchi, K. Endo, Y. Ishikawa, H. Yamauchi, Y.X. Liu, J. Tsukada, K. Sakamoto, and M. Masahara, "Comprehensive analysis of variability sources of FinFET characteristics", VLSI Tech. Dig., 118, 2009.

- [21] http://www.itrs.net/