# Synthesis and Characterization of Ni/Si Nanowires for Electrical Transport

Jae Ho Lee, Michael Carpenter, Eric Eisenbraun, Yongqiang Xue, and Robert Geer

College of Nanoscale Science and Engineering University at Albany, 255 Fuller Road, Albany, NY 12203 E-mail: RGeer@uamail.albany.edu, Phone/Fax: (518) 956-7003/437-8603

# **ABSTRACT**

Self-assembled Si nanowires (SiNWs) have been synthesized and characterized as a template for surface metal silicide formation to investigate confinement of electron transport at the nanowire surface. The SiNWs with diameters ranging from 5 to 180 nm were synthesized via the solid-liquid-solid (SLS) mechanism with a sputtered Au film as catalyst. Post-deposition thermal processing was carried out for silicide formation. Metal-silicide coated wires were dispensed on metal-patterned Si wafers to carry out two-point and four-point electrical conductivity measurements. Electrical contacts were formed via FIBbased Pt deposition. Metal-silicide-coated SiNWs exhibited an improvement in electrical conductivity of several orders of magnitude. Preliminary analyses imply variable thickness of the metal silicide region based, in part, on deposition methodology and thermal process parameters.

*Keywords*: silicon nanowire (SiNW), solid-liquid-solid (SLS), nickel silicide, electrical conductivity

## 1 INTRODUCTION

Semiconductor and metallic nanowires have attracted substantial attention for a variety of nanoelectronic applications. In particular, silicon nanowires (SiNWs) may be an attractive alternative to conventionally processed Si transistors if their intrinsic self-assembly can be harnessed to obviate the need for complex lithographic techniques for device fabrication. In addition, SiNWs can potentially function as both the switch (i.e. transistor) and local interconnect (e.g. metal silicide nanowire) to form an inherently integrated nanoelectronic system – potentially on the same self-assembled nanostructure [1-3].

In terms of metal silicide candidates for such nanostructures, nickel silicide (NiSi) possesses several advantages including low resistivity and low formation temperature [4-7]. In fact, for current CMOS technology NiSi has been shown to be a good electrical contact material for gate, source and drain [8-10]. Recent demonstrations of excellent conductance in NiSi nanowires have also highlighted the excellent potential for SiNW-based systems.

Currently, there are several methods available to synthesize silicon nanowires including laser ablation [1, 11], physical vapor deposition [12], thermal evaporation [13], chemical vapor deposition [14-16], solid-liquid-solid (SLS) growth [17, 18], vapor-liquid-solid (VLS) growth

[19, 20], and oxide assisted growth [21]. The SLS growth is a relatively straightforward technique to synthesize nanowires without a gas phase precursor such as SiH<sub>4</sub> or SiCl<sub>4</sub>. Via the SLS process, silicon nanowires can be directly grown on a silicon substrate which acts as the silicon [17].

In the SLS process, a thin metal film is deposited on a single-crystal silicon substrate (e.g. (100) Si wafer) as a catalyst. Heating of the metallized Si results in metal droplet formation. Continuous diffusion of silicon atoms from the substrate to the droplet at elevated temperatures causes saturation of silicon inside the droplet, and subsequent precipitation at the surface of the droplet. In the presence of a negative temperature gradient at the droplet surface (e.g. due to a gas flow) the surface Si precipitate forms a Si growth front resulting in nanowire formation from the catalyst [17].

In this paper, we report investigations of SLS-grown SiNWs as templates for the surface formation of NiSi to investigate confinement of electron transport at the nanowire surface. Silicon nanowires were grown via the SLS approach on Si (100) and (111) substrates using a sputtered Au film as catalyst in an oxygen-filtered Ar ambient. The influence of annealing time on SLS SiNW growth is discussed in term of nanowire diameter. Postgrowth Ni deposition is followed by variable-rate thermal processing to investigate the surface morphology of nickel silicide formation.

Following thermal processing, NiSi-coated SiNWs underwent electrical conductivity testing within two-point and four-point probe structures processed within a focused ion-beam scanning electron microscope (FIB-SEM).

## 2 EXPERIMENTAL DETAILS

The substrates used were p-type (100) and (111) silicon wafers with electrical resistivity in the 1-10  $\Omega$ •cm range. Wafers were cleaned with diluted hydrofluoric acid (1%) to remove the native oxide layer and ultrasonicated in acctone to remove organic contamination. The cleaned samples were immediately loaded into a PVD (evacuated to  $5\times10^{-7}$  Torr) for sputtering of a 4 nm thick Au catalyst film.

Following Au deposition the silicon samples were placed inside an annealing chamber. The annealing chamber was evacuated to a base pressure of approximately 5 Torr and backfilled with high purity (99.999%) Ar. In order to reduce residual oxygen in the chamber an oxygen filter and a bypass line were configured in the Ar supply.

The total pressure of the system was then raised to atmospheric pressure. The Au/Si sample was annealed at 1000 °C (30 minute ramping time) under Argon (99.999% purity) gas flow at 2,000 sccm. The annealing duration after the temperature ramp was varied from 10 minutes to 120 minutes to investigate the effect of annealing time on the nanowire diameter, length, and overall morphology.

Ni deposition and subsequent thermal processing was carried on as-deposited SLS SiNWs to investigate surface silicide formation. Nickel was deposited on the nanowires via e-beam evaporation (calibrated for an effective blanket film thickness of 150 nm). Nickel deposited SiNW samples were annealed using a rapid thermal annealing system at 550 °C for 5 min and at 600 °C for 5 min with 10 min ramping time to compare resultant SiNW morphologies which were investigated by SEM.

Metal-coated SiNWs and as-grown SiNWs were dispensed on metal-patterned Si wafers to carry out two-point and four-point electrical conductivity measurements. Electrical contacts were formed using Pt deposition within a dual beam FIB-SEM. Structural and compositional properties of these wires were analyzed using SEM, energy dispersive x-ray spectroscopy (EDS), and transmission electron microscopy (TEM).

## 3 RESULTS

The solid-liquid-solid (SLS) method, as described above, was used to synthesize silicon nanowires. The samples were taken out of the annealing furnace after cooling to room temperature. The effects of annealing duration were investigated. The furnace temperature was ramped up to 1,000 °C for 30 min under 2,000 sccm of Ar flow. After the ramp the furnace temperature was held constant for durations ranging from 10 minutes to 120 minutes. Figure 1 shows SEM micrographs of typical SiNWs synthesized for various anneals (1000 °C). An approximately bimodal diameter distribution was observed. Increased annealing time resulted in larger SiNW diameters. SiNWs diameters ranged from 5-22 nm after 10 minute annealing, 45-52 nm after 60 minute annealing, and 77-180 nm after 120 minute annealing.

Si nanowires exhibiting the smallest diameters of 5 nm observed here have not been reported previously (grown via SLS). Typically, small diameter nanowires were only reported for vapor-liquid-solid (VLS) growth when utilizing nm-thick catalyst layers or distributions of nm-scale catalytic particles. In VLS growth, controlling the diameter of nanowires can be achieved by adjusting the precursor and pressure. However, in conventional SLS growth, diameter control is a challenge since SiNW growth is proceeds rapidly at high temperature. In the work reported here, variation of the anneal duration and Ar gas flow rate serve to immediately quench the growth and help regulate SiNW diameter.

After growth, SiNWs were detached from the initial silicon wafer using ultrasonication in a solvent and

distributed on highly oriented pyrolytic graphite (HOPG) substrates to carry out compositional analyses.

Figure 1: SEM micrograph of nanowires synthesized at 1000 °C for (a) 10 min, (b) 15 min, (c) 45 min, (d) 60 min, (e) 90 min, (f) 120 min annealing times. Deposited Au catalyst layer was 4 nm thick.

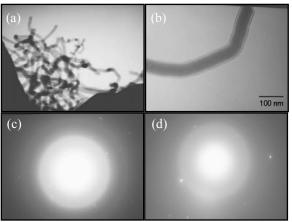

Figure 2: (a) TEM micrograph showing the morphology of a SiNW bundle, (b) Single SiNW, (c), (d) Selected-area electron diffraction (SAED) patterns from SiNWs.

Selected-area electron diffraction (SAED) patterns (Fig. 2(c) and 2(d)) were acquired from individual SiNWs. These implied an amorphous microstructure for the SiNWs evaluated. This implies the possible presence of oxygen in the SiNWs. It should be noted that crystalline nanowires have been typically observed via VLS growth, while SLS methods generally produce amorphous nanowires. This may be due to the fast growth rate and high temperature of the SLS process, which leads to amorphous rather than crystalline growth.

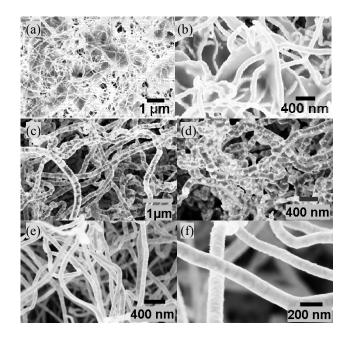

Figure 3: SEM images of Ni-deposited SiNWs: (a), (b) as-deposited; (c), (d) Ni-deposited SiNW after slow annealing at 600 °C for 10 minutes in Ar ambient (c), (d). Note rough surface morphology; (e), (f) Ni-deposited SiNW after rapid thermal annealing at 550 °C for 5 minutes in N<sub>2</sub> ambient. Note smooth morphology.

Nickel was deposited on the nanowires by e-beam evaporation calibrated for an effective blanket film thickness of 150 nm. Post-deposition thermal processing was carried out for nickel silicide formation (550 °C for 5 minutes via RTA and 600 °C for 5 minutes with a 10 minute ramp). Post-anneal nanowire surface morphology was sensitive to anneal temperature and ramp rate. Rapid ramps resulted in an atomically-smooth Ni-SiNW template morphology. Slow annealing resulted in a rough Ni-SiNW surface morphology indicative of nonuniform silicide domain formation, as shown in Fig. 3.

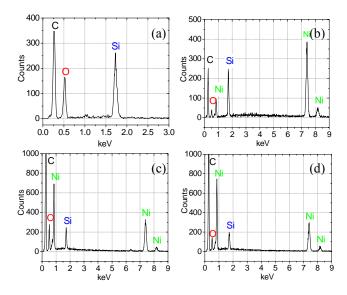

Energy dispersive x-ray spectroscopy (EDS) was performed for post-annealed Ni-deposited SiNWs on an HOPG substrate for compositional analysis. Figure 4 shows EDS spectra of nanowires on the initial silicon substrate, after Ni deposition, after slow annealing, and after RTA (the latter three on HOPG substrates). The results confirm the presence of nickel on individual SiNWs after thermal processing. Note the substantial increase of the La peak (0.85 keV) relative to the Ka peak (7.47 keV) for the annealed Ni-SiNWs. This implies nickel silicide formation [6, 22, 23]. The EDS data in Fig. 4 also confirm the presence of oxygen in the SiNWs.

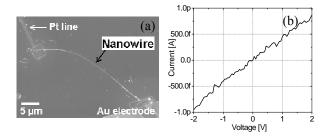

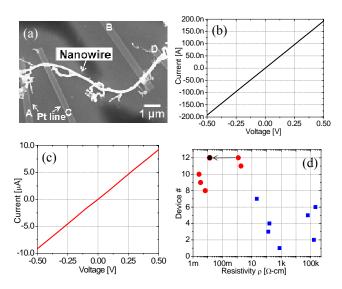

As-grown silicon nanowires and metal-silicide coated SiNWs were dispensed on SiO<sub>2</sub>-coated Si wafers patterned with a metal (Au) electrode pattern to carry out electrical conductivity measurements. Electrical connection between the dispensed SiNWs and the Au electrodes were formed via direct-write FIB-based Pt deposition. Figures 5a and 5b

show an SEM micrograph and associated current-voltage characteristic of an as-grown SiNW, respectively. The I-V response of the SiNW is linear and the two-point resistivity of similar SiNWs ranged from  $20~\Omega \cdot \text{cm}$  to  $2\times 10^5~\Omega \cdot \text{cm}$ . The observed electrical resistivity range for as-deposited SiNWs rules out a dominant SiO<sub>2</sub> stoichiometry, although it is not inconsistent with local SiO<sub>x</sub> compositions within the nanowire. (No current measurement was possible for open Pt electrodes confirming the insulative properties of the SiO<sub>2</sub> dielectric in the electrical test structure.)

Figure 4: EDS spectra of nanowires: (a) as-grown nanowire on the initial silicon substrate; (b) after Ni deposition (on HOPG); (c) after slow annealing (on HOPG); (d) after rapid annealing (on HOPG).

Figure 5: Pt deposition and I-V measurement of dispensed as-grown silicon nanowire. (a) SEM image of the wire connected by Pt lines on Au-patterned oxide substrate, nanowire length was 29  $\mu$ m and diameter was 168 nm. (b) I-V characteristics.

The resistivity of post-annealed Ni-SiNW wires was measured by two- and four-point electrical conductivity measurements, as shown in Fig. 6. Two- (Fig. 6a) and four- (Fig. 6c) point I-V measurements yield resistance of 2 M $\Omega$  and 55 k $\Omega$ , respectively, for the 9.2 µm long device with a diameter of 165 nm, which corresponds to a resistivity of 0.47  $\Omega$ ·cm and 0.013  $\Omega$ ·cm, respectively.

Fig. 6 (d) shows calculated resistivity from as-grown nanowires and metal-silicide coated wires. It is clear that after post-deposition of nickel on the silicon nanowires the conductivity is increased up to 7 orders.

Figure 6: (a) SEM image of metal-silicide coated wire with four terminals, (b) I-V characteristics via two-point measurement, (c) via four-point measurement, (d) calculated resistivity from as-grown nanowires (blue squares) and metal-silicide coated wires (red circles).

# 4 CONCLUSION

Self-assembled Si nanowires were synthesized and characterized as a template for surface metal silicide formation to investigate confinement of electron transport at the nanowire surface. Silicon nanowires with diameters ranging from 5 to 180 nm were synthesized via solid-liquid-solid (SLS) growth. The diameter of as-grown SiNWs can be controlled, to an extent, through the annealing time.

Post-growth Ni deposition and thermal processing was carried out for nickel silicide formation at the SiNW surface. Post-annealed Ni-SiNW surface morphology was sensitive to anneal temperature and ramp rate. Rapid ramps resulted in an atomically smooth Ni-SiNW surface morphology. Slow annealing resulted in a rough Ni-SiNW surface morphology indicative of nonuniform domain formation. EDS measurements confirm that the nickel remains on the SiNW surface after thermal processing. Also, the substantial increase of the La peak (0.85keV) relative to the Ka peak (7.47 keV) in the EDS spectra for the annealed Ni-SiNWs implies nickel silicide formation.

Metal-silicide coated wires were dispensed on metalpatterned Si wafers to carry out two-point and four-point electrical conductivity measurements. Electrical contacts were formed via FIB-based Pt deposition. Metal-silicidecoated SiNWs exhibited an improvement in electrical conductivity of several orders of magnitude compared with that of as-grown silicon nanowires.

## **ACKNOWLEDGEMENTS**

This work was supported by the Semiconductor Research Corporation Focus Center Research Program, the Nanoelectronics Research Corporation, and the New York State Office of Science, Technology and Academic Research.

# **REFERENCES**

- [1] A. M. Morales and C. M. Lieber, Science, 279 (9), 208, 1998.

- [2] W. Lu and C. M. Lieber, Nature Mater. 6, 841, 2007.

- [3] A. Colli, A. Fasoli, P. Beecher, P. Servati, S. Pisana, Y. Fu, A. J. Flewitt, W. I. Milne, J. Robertson, C. Ducati, S. De Franceschi, S. Hofmann and A. C. Ferrari, J. of Appl. Phys., 102, 034302, 2007.

- [4] Y. Wu, J. Xiang, C. Yang, W. Lu and C. M. Lieber, Nature, 430, 61-65, 2004.

- [5] X. W. Zhang, S. P. Wong, W. Y. Cheung and F. Zhang, Mat. Res. Soc. Symp. 611, C6.5.1, 2000.

- [6] J. Kim and W. A. Anderson, Thin Solid Films, 483, 60, 2005.

- [7] G. B. Kim, D. J. Yoo, H. K. Baik, J. M. Myoung, S. M. Lee, S. H. Oh and C. G. Park, J. Vac. Sci. Technol. B 21, 319, 2003.

- [8] C. Lavoie, F. M. d'Heurle, C. Detavernier and C. Cabral, Microelectronic. Eng. 70, 144, 2003.

- [9] J. A. Kittl, A. Lauwers, O. Chamirian, M. Van Dal, A. Akheyar, M. De Potter, R. Lindsay and K. Maex, Microelectronic. Eng. 70, 158, 2003.

- [10] T. Morimoto, T. Ohguro, S. Momose, T. Iinuma, I. Kunishima, K. Suguro, I. Katakabe, H. Nakajima, M. Tsuchiaki, M. Ono, Y. Katsumata, H. Iwai, IEEE Trans. Electron Devices, 42, 915, 1995.

- [11] Y. F. Zhang, Y. H. Tang, N. Wang, D. P. Yu, C. S. Lee, I. Bello and S. T. Lee, Appl. Phys. Lett. 72, 1835, 1998.

- [12] N.D. Zakharov, P. Werner, G. Gerth, L. Schubert, L. Sokolov and U. Gösele, J. Cryst. Growth, 290, 6, 2006.

- [13] D. P. Yu, Z. G. Bai, Y. Ding, Q. L. Hang, H. Z. Zhang, J. J. Wang, Y. H. Zou, W. Qian, G. C. Xiong, H. T. Zhou and S. Q. Feng, Appl. Phys. Lett. 72, 3458, 1998.

- [14] J. Westwater, D. P. Gosain, S. Tomiya, S. Usui, and H. Ruda, J. Vac. Sci. Technol. B 15, 554, 1997.

- [15] Yi Cui, L. J. Lauhon, M. S. Gudiksen, J. Wang and C. M. Lieber, Appl. Phys. Lett. 78, 2214, 2001.

- [16] A. I. Hochbaum, R. Fan, R. He and P. Yang, Nano Lett. 5, 457, 2005.

- [17] Maggie Paulose, Oomman K. Varghese and Craig A. Grimes, J. Nanosci. Nanotech. 3, 341, 2003

- [18] H. F. Yan, Y. J. Xing, Q. L. Hang, D. P. Yu, Y. P. Wang, J. Xu, Z. H. Xi and S. Q. Feng, Chem. Phys. Lett. 323, 224, 2000.

- [19] R. S. Wagner, W. C. Ellis, Appl. Phys. Lett. 4, 89, 1964.

- [20] E. I. Givargizov, J. Cryst. Growth, 31, 20, 1975.

- [21] R. Q. Zhang, Y. Lifshitz and S. T. Lee, Adv. Mater. 15 (7-8), 635, 2003.

- [22] Y. Song and S. Jin, Appl. Phys. Lett. 90, 173122, 2007.

- [23] K. S. Lee, Y. H. Mo, K. S. Nahm, H. W. Shim, E. K. Suh, J. R. Kim and J. J. Kim, Chem. Phys. Lett. 384, 215, 2004.