# **Optimal Skew Corners for Compact Models**

Ning Lu

IBM Semiconductor Research and Development Center, Systems and Technology Group, Essex Junction, VT 05452 USA lun@us.ibm.com

#### **ABSTRACT**

We describe an innovative approach to generate an optimal skew corner of a compact device model (e.g., a Spice model) for a single performance target, and to generate a common/optimal corner of a compact device for multiple performance targets. We also analyze the existence condition of a common/optimal corner.

*Keywords*: Spice modeling, statistical modeling, skewing in compact models, corner models, worst-case model

### 1 INTRODUCTION

Compact models of semiconductor devices are often enabled with Monte Carlo simulation capability. To save circuit simulation time, it is often desirable to have a worstcase skew-corner library for simulating the worst-case behavior of the circuit [1-4]. We present an innovative approach to generate an optimal skew corner of a compact/Spice device model for a single performance target, and to generate a common/optimal skew corner of a compact model for multiple performance targets. An optimal skew corner is such a skew corner that has the largest joint probability density (JPD) among multiple corners or is a least-squares fitting corner. Each statistical parameter of the model is properly skewed within its tolerance range in such a way that the model will reproduce the fast/slow corner results of one or multiple performance targets while maximizing the JPD. The existance conditions of a common/optimal corner are analyzed.

The corner model problem of N targets and M statistical model parameters is solved based on the sensitivities  $a_{ij}$  (of the ith target on the jth parameter) in the first-order approximation. The corner model problem in the case of two statistical parameters (M = 2) is also solved graphically.

## 2 CORNER MODEL METHODOLOGY

I. In the original coordinate system. For a given compact device model of M independent statistical model parameters  $x_1, x_2, ..., x_M$  and a given operating point (e.g., device length and width, voltage biases, temperature, etc.), we obtain a first-order approximation for each of N performance targets  $F_i(x_1, x_2, ..., x_M)$  around its nominal performance value  $F_{i0} = F_i(x_{10}, x_{20}, ..., x_{j0}, ..., x_{M0})$ ,

$$F_i(x_1, ..., x_M) = F_{i0} + \sum_{j=1}^{M} a_{ij}(x_j - x_{j0}), \quad i = 1, 2, \dots, N, (1)$$

where  $x_{j0}$  is the nominal value of the *j*th model parameter  $x_j$ , and the coefficient  $a_{ij}$  (j = 1, 2, ..., M) is the sensitivity of the *i*th performance target  $F_i$  with respect to the *j*th model

parameter  $x_j$  at the given operating point. The JPD for the M independent statistical parameters is

$$P(x_1,...,x_M) = \prod_{j=1}^{M} \frac{1}{\sqrt{2\pi}\sigma_j} \exp \left[ -\frac{1}{2} \frac{(x_j - x_{j0})^2}{\sigma_j^2} \right], (2)$$

where  $\sigma_j$  is the standard deviation of the *j*th statistical model parameter  $x_i$ . The variance of the *i*th target  $F_i$  is thus

$$S_i^2 \equiv \left\langle F_i^2 \right\rangle - \left\langle F_i \right\rangle^2 = \sum_{i=1}^M a_{ij}^2 \sigma_j^2, \quad i = 1, 2, \dots, N.$$

(3)

Relation (3) links the standard deviation  $S_i$  of the *i*th circuit performance target to the standard deviations  $\sigma_i$  of the compact model parameters. The k- $\sigma$  (k = 1, 2, 3, ...) best/worst case of  $F_i$  is ( $F_{i0} + k\eta_i S_i$ ) with  $\eta_i$  being 1 (for an upper bound) or -1 (for a lower bound). In order to reach a k- $\sigma$  best/worst case performance corner, the model parameters should take values within their respective tolerance range [ $x_{i0} - k\sigma_i, x_{i0} + k\sigma_i$ ].

<u>II. In a normalized coordinate system.</u> First, we introduce normalized sensitivity coefficients

$$\alpha_{ij} = a_{ij} \sigma_j / S_i, \qquad i = 1, 2, ..., N, \quad j = 1, 2, ..., M.$$

(4)

The coefficients  $\alpha_{ij}$  and  $a_{ij}$  are of the same sign. Introducing a set of vectors  $\vec{\alpha}_i = (\alpha_{i1}, \alpha_{i2}, \dots, \alpha_{iM})^T$  in the *M*-dimensional model parameter space  $(u_1, u_2, \dots, u_M)$  and using (3) and (4), we find that the length of each vector is 1,  $\vec{\alpha}_i \cdot \vec{\alpha}_i = 1$ ,  $i = 1, 2, \dots, N$ . (5)

Equation (5) shows that each of normalized sensitivity coefficients is bounded,  $-1 \le \alpha_{ij} \le 1$ , j = 1, 2, ..., M.

Next, we introduce a shifted-and-scaled coordinate system,

$$u_{i} = (x_{i} - x_{i0})/(k\sigma_{i}), \quad j = 1, 2, ..., M,$$

(6)

which is dimensionless. Notice that  $u_j = 0$  means that the model parameter  $x_j$  is at its nominal value  $x_{j0}$ , and  $|u_j| \le 1$  corresponds to the model parameter  $x_j$  within its k- $\sigma$  tolerance range,  $x_{j0} - k\sigma_j \le x_j \le x_{j0} + k\sigma_j$ . The JPD (2)

becomes

$$P \propto \exp(-k^2 \vec{u} \cdot \vec{u}/2)$$

, where  $\vec{u} = (u_1, \dots, u_M)^T$ .

The JPD peaks at the origin  $\vec{u}=0$ . Moving away from the origin, the JPD decreases rapidly. An equal probability surface is a sphere in the the *M*-dimensional model parameter space. So, the closer a point is to the origin  $\vec{u}=0$ , the higher the joint probability density *P*.

Using Eqs. (1), (4), (6), and the above mentioned best/worst case of performance targets  $F_i$ , we obtain N linear equations for determing the M corner model parametes,

$$\vec{\alpha}_i \cdot \vec{u} = \eta_i , \qquad i = 1, 2, ..., N . \tag{7}$$

Geometrically, each equation in (7) represents a plane in the M-dimensional model parameter space whose distance to the center of the normalized coordinate system is 1 and, for the ith target, the normal direction of the plane is  $\vec{\alpha}_i$ . In other words, each plane is tangent to a unit sphere in the M-dimensional space, and the unit sphere is an equal probability surface. Each plane is also a plane of constant value of  $F_i$ . In the two-parameter case (M = 2), the M-dimensional model parameter space simplifies to a two-dimensional plane, the unit sphere reduces to a unit circle, and the plane becomes a straight line (Figs. 1–3).

## 3 OPTIMAL CORNER FOR A SINGLE TARGET

Often we need to provide N separate skew corners, i.e., one skew corner for the best or worst case value of target  $F_1$  only, and another skew corner for the best or worst case value of target  $F_2$  only, etc.

I. Typical non-optimal corner solution. A typically used method is to skew all statistical model parameters together in the same percentage amount through the use of a corner parameter (say, cor), namely, to set  $|u_1| = |u_2| = \cdots$  =  $|u_M| = \cos r/3$ . In this approach, the corner solution for the *i*th circuit performance target is found from Eq. (7) to be  $u_j^{(1)} = \eta_i \operatorname{sgn}(\alpha_{ij}) / \sum_{m=1}^M |\alpha_{im}|$ , j = 1, 2, ..., M. The superscript (1) indicates a 1<sup>st</sup> order solution of the corner problem. When projected to a two-parameter sub-space, this corresponds to moving out in the 45° direction in the nomalized coordinate system. This method usually does not give an optimal skew corner. In general, any point on the *i*th plane in (7) is a corner point for the *i*th target. Most of them, however, are not optimal corners.

<u>II. Optimal corner solution.</u> By comparing Eq. (7) with Eq. (5), we find that

$$\vec{u}^{(1)} = \eta_i \vec{\alpha}_i \tag{8}$$

are a set of solutions (of unequal percentage amount of skewing) for the *i*th target. Equation (8) says that the amount of skewing,  $u_j^{(1)}$ , for each parameter  $x_j$  is proportional the normalized sensitivity  $\alpha_{ij}$ . If a particular model parameter  $x_j$  has no effect on a performance target, then it should stay at its nominal value,  $x_j = x_{j0}$ , for the corner of that performance target. Using Eq. (5) and noting that  $\eta_i$  is either 1 or -1, we find that the length of the skew-corner vector solution (8) is 1,  $\vec{u}^{(1)} \cdot \vec{u}^{(1)} = 1$ . This shows that solution (8) is on the unit sphere in the *M*-dimensional space and thus is the optimal solution, since it has the

shortest distance 1 to the center of the sphere, i.e., the largest JPD among all corner solutions. Further, each of solution components is bounded,  $-1 \le u_i^{(1)} \le 1$ .

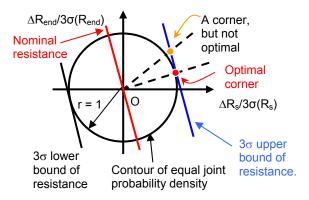

III. Two-parameter example. Figure 1 is an example of a diffused resistor. Sheet resistance  $R_s$  and end resistance  $R_{end}$ are two (main) statistical model parameters typically. The origin O in Fig. 1 represents nominal for all parameters. The unit circle is a contour of equal JPD (k = 3). The JPD outside the unit circle is smaller than the JPD on the unit circle. Resistance value increases with increasing sheet and/or end resistance. Both "lines of  $3\sigma$  upper and lower bounds of resistance" (resistance target lines) are targent lines of the unit circle, and are parallel to each other. Any point on one of two resistance target lines is a corner point, but most of them are not optimal corners. The intersection of the 45° line and a resistance target line is a typical nonoptimal corner solution discussed in I. The optimal corner is on the unit circle, since it has the shortest distance to the center of the circle.

Figure 1: Diffused resistor: Resistance variations and corners in the space of sheet resistance & end resistance.

## 4 COMMON/OPTIMAL CORNER FOR MULTIPLE TARGETS

If one wants to find a common corner in the the M-dimensional space for N performance targets  $F_i$  simultaneously, then N equations in (7) must be satisfied simultaneously. In the following we discuss the solutions of Eq. (7) in 3 separate situations.

<u>I. Situation of N = M.</u> When the number of performance targets N equals the number of model parameters M, the M linear algebraic equations (7) uniquely determine M corner coordinates  $u_1^{(1)}$ ,  $u_2^{(1)}$ , ...,  $u_M^{(1)}$ . When all ratios  $\alpha_{il}/\eta_i$  (i = 1, 2,..., N) have the same sign (or being zero), and all ratios  $\alpha_{i2}/\eta_i$  (i = 1, 2,..., N) have the same sign (or being zero), etc., the solution will be bounded,  $-1 \le u_j^{(1)} \le 1$  (j = 1, 2,..., M), and the sign of  $u_i^{(1)}$  is the same as that of  $\alpha_{ij}/\eta_i$ .

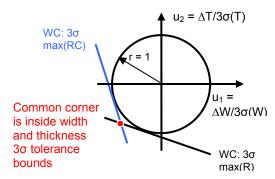

Figure 2 shows an interconnect example with N = M = 2. Wire resistance R increases with decreasing wire width W and/or wire thickness T, so does the product RC of wire

resistance R and capacitance C. Each of  $\eta_1$  and  $\eta_2$  is 1, since each target is an upper bound target. Both  $\alpha_{11}/\eta_1$  and  $\alpha_{21}/\eta_2$  have the same sign (negative), and both  $\alpha_{12}/\eta_1$  and  $\alpha_{22}/\eta_2$  are of the same sign (negative), and the common corner  $(u_1^{(1)}, u_2^{(1)})$  of  $3\sigma$  worst-case (WC) R and  $3\sigma$  WC RC is located within the  $3\sigma$  tolerance bounds of wire width W and wire thickness T,  $|u_j^{(1)}| < 1$ . In addition, the sign of  $u_1^{(1)}$  is the same as that of  $\alpha_{11}/\eta_1$  and  $\alpha_{21}/\eta_2$  (negative), and the sign of  $u_2^{(1)}$  is the same as that of  $\alpha_{i2}/\eta_i$  (negative).

Figure 2: Interconnect resistance *R* and interconnect delay *RC* in the space of wire width and wire thickness.

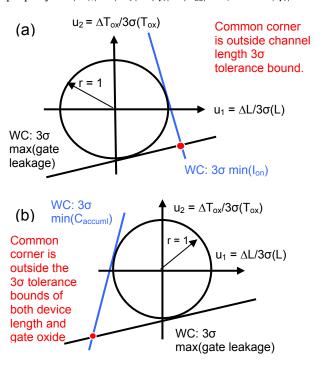

Figure 3(a) shows a FET example with N=M=2. FET drain current decreases with increasing channel length L ( $\alpha_{11} < 0$ ) and/or increasing gate oxide thickness  $T_{\rm ox}$  ( $\alpha_{12} < 0$ ). FET gate leakage increases with increasing channel length L ( $\alpha_{21} > 0$ ) and/or decreasing gate oxide thickness  $T_{\rm ox}$  ( $\alpha_{22} < 0$ ). For the lower bound of FET current,  $\eta_1 = -1$ . For the upper bound of gate leakage,  $\eta_2 = 1$ . So, the two different performance targets lead to the same sign (positive) between  $\alpha_{11}/\eta_1$  and  $\alpha_{21}/\eta_2$ , but opposite signs between  $\alpha_{12}/\eta_1$  (positive) and  $\alpha_{22}/\eta_1$  (negative). The common corner is outside channel length bound,  $|u_1^{(1)}| > 1$ , which may not be desirable (the JPD at the corner is usually too low). One may want to use two separate corners, one for the drain current only and the other for the gate leakage only.

Figure 3(b) illustrates a MOS varactor example of N=M=2. The accumulation capacitance decreases with decreasing device length L ( $\alpha_{11}>0$ ), increasing gate oxide thickness  $T_{\rm ox}$  ( $\alpha_{12}<0$ ). For the lower bound of accumulation capacitance,  $\eta_1=-1$ . Here, the two different performance targets give opposite signs between  $\alpha_{11}/\eta_1$  (negative) and  $\alpha_{21}/\eta_2$  (positive), and opposite signs between  $\alpha_{12}/\eta_1$  (positive) and  $\alpha_{22}/\eta_1$  (negative). Thus, both  $|u_1^{(1)}|$  and  $|u_2^{(1)}|$  are larger than 1, and the common corner is not desirable (extreamly low JPD). Two separate corners are needed.

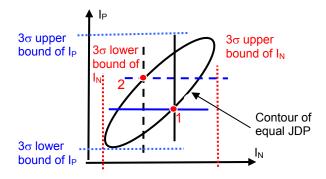

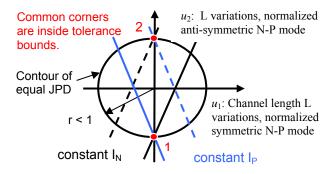

Figure 4 shows fast-NFET—slow-PFET (fNsP) and slow-NFET—fast-PFET (sNfP) corners for the saturation current of a pair of NFET and PFET. The variations of NFET and PFET channel length are partially correlated. These coupled

variations (plus the variations of  $T_{ox}$ , threshold voltage, etc.) give the ellipses in Fig. 4. Figure 5 illustrates the corresponding common corners in the space of FET channel length variations. The ellipse in Fig. 4 becomes the circle in Fig. 5, and two solid (dashed) lines in Fig. 4 remain as two solid (dashed) lines in Fig. 5. We use the principal component analysis to decompose the N-P channel length variations into a symmetric N-P component  $(u_1)$  and an anti-symmetric component  $(u_2)$ . After a normalization, the variations of NFET and PFET normalized currents are  $\Delta I_{N,P} = \alpha_{21}u_1 \mp \alpha_{22}u_2 + \dots = \eta_{1,2}$ , where we have used  $\alpha_{11}=\alpha_{21}$  and  $\alpha_{12}=-\alpha_{22}$  . For the fNsP and sNfP corners in Fig. 4, we have  $\Delta I_N = -\Delta I_P$ , namely,  $\eta_1 = -\eta_2$ . Here  $\alpha_{11}/\eta_1$  and  $\alpha_{21}/\eta_2$  are of opposite signs. In spite of this and different from Fig. 3(a), we still get  $|u_i|^{(1)} \le 1$  as desired. The reason is that, in this highly correlated case, we have properly set  $|\Delta I_N| = |\Delta I_P| = |\eta_1| = |\alpha_{22}| < 1$ , not set  $|\eta_1| = 1$ .

Figure 3: Common corners outside tolerance bounds due to the opposite moving directions w.r.t. process parameters. (a) FET: Worst-case drain current and gate leakage current. (b) MOS varactor: Worst-case accumulation capacitance and gate leakage.

<u>II. Situation of N > M.</u> When N > M, there are more equations than unknowns, and we use a least-squares fit method to find an optimum set of  $\vec{u}$ . We minimize  $\sum_{i=1}^{N} (\vec{\alpha}_i \cdot \vec{u} - \eta_i)^2$ . Setting each of M first-order derivatives w.r.t.  $u_j$  to zero, we obtain M linear algebraic equations. Solving the M linear algebraic equations, we find the values of M variables  $u_1, u_2, ..., u_M$ .

Figure 4: Schematic plot of NFET current vs. PFET current distribution. Point 1 is a fast-NFET, slow-PFET (fNsP) corner, and point 2 is a slow-NFET, fast-PFET (sNfP) corner.

Figure 5: For fNsP and sNfP points in Fig. 4, their optimal and common corner solutions in the N-P channel length plane of model parameter space.

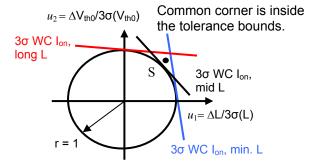

A FET example of N=3 and M=2 is given in Fig. 6. At a fixed nominal channel length L, FET saturation current  $I_{\rm on}$  decreases with increasing channel length variation  $\Delta L$  and threshold voltage parameter  $V_{\rm th0}$ . As the nominal channel length L increases,  $I_{\rm on}$  becomes more sensitive to the variation  $\Delta V_{\rm th0}$  in threshold voltage parameter and less sensitive to the channel length variation  $\Delta L$ . An optimal corner S for the three WC  $I_{\rm on}$  targets of different channel lengths is found at the center of a triangle formed by the three WC  $I_{\rm on}$  target lines. The least-squares solution point S of the three  $I_{\rm on}$  lines satisfy  $0 < u_1(S), u_2(S) < 1$ .

III. Situation of  $N \le M$ . There are many corner solutions in this situation. We find the optimal solution by maximizing the JPD (2) subject to the N constraints as given by Eqs. (7). Namely, we minimize  $\vec{u} \cdot \vec{u} + \sum_{i=1}^{N} \lambda_i (\vec{\alpha}_i \cdot \vec{u} - \eta_i)$ . Setting each of M first-order derivatives w.r.t  $u_j$  to zero, we have M linear equations. Setting each of another N first-order derivatives w.r.t.  $\lambda_i$  to zero, we re-get N linear equations in Eq. (7). We solve (M + N) linear algebraic equations and get (M + N) variables  $u_1, ..., u_M, \lambda_1, ..., \lambda_N$ .

The single-target case (N = 1) discussed in Sec. 3 is a special case of this situation. Solution (8) is a set of optimal solutions (for a single target problem), since it maximizes the joint probability distribution.

Figure 6: A least-squares common corner of FET  $I_{on}$  for 3 different channel lengths in the space of channel length and thresold voltage variations.

### 5 HIGHER-ORDER SOLUTION

After obtaining the first-order solution, we further construct a  $2^{\text{nd}}$ -order (i.e., quadratic response surface) approximation to the performance targets. Then, we use the above first-order solution as the starting point of an iteration solution process to solve a set of non-linear (say, quadratic) equations. In this approach, we obtain a set of more accurate corner solution,  $u_1^{(2)}$ ,  $u_2^{(2)}$ , ...,  $u_M^{(2)}$ .

#### 6 SUMMARY

We have described an innovative approach to generate an optimal skew corner of a compact device model (Spice model) for a single performance target, and to generate a common/optimal corner of a compact device for multiple performance targets. The optimal corners are found by maximizing the joint probability density. The existence condition of a common/optimal corner is discussed. The approach presented here can also be applied to the corner modeling analyses of circuit simulations, higher-level logic cell/block delay, timing closure, etc.

#### ACKNOWLEDGMENT

The author would like to thank Josef Watts for valuable manuscript improvement suggestions.

### REFERENCES

- [1] A. Dharchoudhury and S. M. Kang, *IEEE Trans. Computer-Aided Design*, Vol. 14, pp. 481, 1995.

- [2] M. Sengupta, et al., *IEEE Trans. Computer-Aided Design*, Vol. 24, No. 9, pp. 1372-1380, 2005.

- [3]. J. Watts, N. Lu, C. Bittner, S. Grundon, and J. Oppold, *Proc. NSTI Nanotech 2005, Workshop on Compact Modeling*, pp. 87-92.

- [4] N, Lu, Proc. IEEE Custom Integrated Circuits Conference, pp. 853–856, 2006.