# **Optimization of Disk-type Piezoelectric Transformers**

Chi-Wei Kuo, Chia-Yu Kang, Ying-Yin Huang, \*Chih-Kung Lee, and Yao-Joe Yang

Department of Mechanical Engineering, National Taiwan University

\*Institute of Applied Mechanics, National Taiwan University

ADDRESS: No. 1, Roosevelt Rd., Sec. 4, Taipei, Taiwan EMAIL: kuoway@mems.me.ntu.edu.tw

# **ABSTRACT**

In this work, we present the optimization works of two disk-type piezoelectric transformers (PTs), the singleoutput PT and the dual-output PT, by using the elite Genetic Algorithm (GA) and a finite-element solver. The design goal is to maximize the efficiency under the constraint that the voltage gain is greater than 50 for igniting CCFL. The design parameters are the dimensions of the output-electrode sections, the electrode areas, and the devices structure. With different electrical loading impedances, the voltage gain and the efficiency were computed using the finite element solver, NTUPZE. The results were also verified with measured data. optimization process is parallelized by the MPI library and a PC cluster for improving the computation efficiency. The characteristics of the optimal designs with different loads are also calculated.

*Keywords*: Genetic algorithm (GA), piezoelectric transformer, finite element method (FEM), multi-object optimization, parallel computations.

## 1 INTRODUCTION

Recently, liquid crystal displays (LCD) have become one of the standard digital output devices for personal/portable computers as well as consumer electronics. Also, LCD technology is proved to be one of the most promising technologies for the flat-panel TV. Each LCD panel requires a few cold cathode fluorescent lamps (CCFL) as backlight sources. A CCFL requires a high voltage source for ignition. Piezoelectric transformers (PT), which were proposed in 1954 by Rosen [1], step up or step down input voltages by electrical/mechanical/electrical PTs have been proved to be promising conversion. alternatives for magnetic transformers, which are widely used in the LCD devices, because they have several advantages, such as low profile, high efficiency (low loss), no electromagnetic radiation, nonflammable, low harmonic current noise, low temperature rise, and so on.

The PT performance parameters, such as voltage gain, efficiency and power density, are influenced by several factors, including material properties, electrical loadings, electrode shapes, device dimensions, and so on [2]. Traditional optimization approaches, such as the gradient method, the random search method, and the golden-ratio search method, require accurate analytical or compact models of those performance parameters for evaluating necessary information for search direction [3]. A few PT

modeling/design works used equivalent circuit models (compact models) to consider the influences of these parameters [4]. However, the equivalent circuit models are insufficient to study many geometrical aspects of designs. such as the device dimensions and electrode shapes. In addition, accurate analytical or compact models are usually unavailable for the devices with arbitrary shapes. Therefore, in [5], FEM solver and the multimodal function optimization technique are used to optimize the power density and the efficiency of PT. In this work, we will present the development of the optimization platform based on the GA and the FEM techniques. We use the FEM modeling approach (i.e., NTUPZE [6]) to accurately estimate the performance parameters, and then employ the Genetic Algorithm (GA) as the optimization strategy because it can fully utilize the advantages when using FEM approaches.

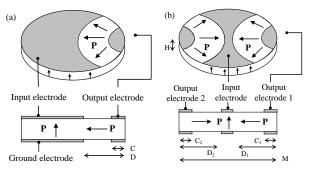

The design goal is to maximize the efficiency under the constraint that reach the required voltage gain for igniting cold-cathode-fluorescent lamps (CCFL) used in LCD backlighting modules. Using the optimization platform, the optimization for two disk-type PTs, the single-output PT [7] and the dual-output PT (Figure 1), will be demonstrated. All of the optimization process is implemented in C++, including the piezoelectric solver NTUPZE and the GA procedure.

Figure 1: The schematic views of (a) a disk-type single-input PT and (b) a disk-type dual-output PT.

It has to be emphasized that standard GA sometimes converges to local optimal points (non-optimal point). The elite GA, one of the variants of typical GAs, can ensure evolutionary processes converge to the global optimum. The basic principle of the elite GA is that the best chromosome of each generation is reserved as one of the chromosomes of the next children generation. Our preliminary study shows that when the elite GA was not

employed, different optima were obtained even in the same search space. Therefore, in this work, we use the elite GA for optimizing PTs.

As we will discuss in the next section, the GA process requires intensive computations. As a result, we also parallelized the GA process using a PC cluster in order to speed up the optimization. By using the MPI libraries, the parallel calculations are implemented by dynamically balancing the workload in every generation and using the manager-worker paradigm [8].

### 2 OPTIMIZATION SCHEME

### 2.1 The Genetic Algorithms

GAs optimize a set of parameters (a chromosome) using adaptive search procedures based on the mechanisms of natural evolution. There are many GA evolution strategies which influence the convergence efficiency. In this work, the design goal is to maximize the efficiency under the constraint that the voltage gain is greater than 50 for igniting CCFL. Therefore, we formulate the cost function as two parts: the penalty function and the compromise function. The penalty function is defined as Equation (1):

$$\lambda(G) = 1 + \exp(-\alpha \times \frac{G - G^*}{G^*}) \tag{1}$$

where G is a computed voltage gain, and  $G^*$  is the required voltage gain.  $\alpha$  is a constant which determines the steepness of the curve. In this work,  $\alpha$  is equal to 100. Obviously, when a chromosome performs a voltage gain (G) lower than  $G^*$ , the penalty function will be much larger than 1, which eliminates the chromosome during the evolution process.

The compromise function calculates the distance between a solution and an ideal solution. The ideal solution is pre-defined by designers. A shorter distance indicates that a better solution is evaluated. The compromise function is defined as Equation (2):

$$r(e) = \frac{e^* - e}{e^*} \tag{2}$$

where e is a computed efficiency, and  $e^*$  is the ideal efficiency, which should be always equal to 100%. The cost function is the product of the penalty function and the compromise function, as shown in Equation (3):

$$cost = \lambda \cdot r \tag{3}$$

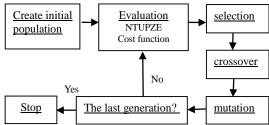

In this work, each of the design parameters will be encoded in a binary chromosome. A generation generates a new population from previous population. Therefore, the generation number is in fact the number of GA evolutions. Mutation is the occasional random alteration in a chromosome. Figure 2 shows the flowchart of the genetic algorithm. The GA parameters for each case presented in the work were the same. The initial population includes 40 chromosomes which are randomly created. The

corresponding efficiency and voltage gain for each chromosome are evaluated. Based on the value of the cost function, 80% of chromosomes are selected for reproduction. A mutation ratio of 0.08 is used for the crossover operation. The selected chromosomes are randomly arranged in pairs, and a single point crossover operation is employed. After the crossover operations, a new generation is created. Then the same procedure repeats until the design parameters converge.

Figure 2: The flowchart of the Genetic algorithm.

### 2.2 Parallelization of GA

In our GA procedure, every chromosome requires an NTUPZE computation to evaluate the corresponding cost values. Computing 40 chromosomes for each generation require significant computational cost, so we employ a PC cluster to reduce total computation time. Through the evolution process, the chromosome population in a generation will converge. Considering the above reasons, the run-time allocation of tasks is employed. The parallel algorithm is based on manager-worker paradigm.

# 3 RESULTS AND DISCUSSIONS

#### 3.1 Single-output PT with Crescent-Shaped Electrode

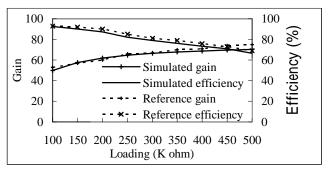

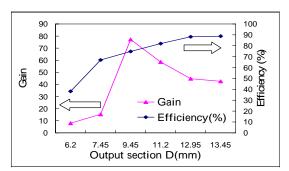

As shown in Figure 1, the single-output PT is a disktype single-layered piezoelectric transformer with an asymmetric-crescent-shaped input electrode and an elliptically-shaped output electrode. The details of the device can be found in [7]. The design parameters are the radius of the output section (D) and the radius of the output electrode (C). Figure 3 shows comparison of the simulated FEM results by using the NTUPZE and the measured results published in [7]. This figure verifies the accuracy of the NTUPZE.

In this case,  $G^*$  is equal to 50. The dimensions of PT are 25.4 mm in diameter and 1.0 mm in thickness. The resistive load is fixed at  $100~k\Omega$  (the typical CCFL impedance) during the GA optimization process. The design space is as follows: the output radius is from 5.7 mm to 13.7 mm and the electrode radius is from 1.7 mm to 8.7 mm. The material properties are listed in Appendix A.

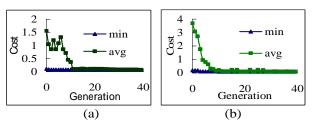

Figure 4(a) shows the convergence performance of GA for this case. The optimized results for the radius of the output section (D) and the radius of output electrode (C) is 12.70mm and 4.11mm, respectively. The corresponding voltage gain and efficiency are 53.8 and 91.9%, respectively. Also, as shown in Figure 5, we found that the higher the output section radius, the higher the efficiency.

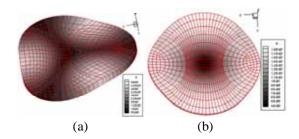

However, voltage gain is not necessarily higher. Figure 6(a) shows the deformed shape of the optimal design operating at resonance frequency. The GA parameters and the optimized results are listed in Table 1.

Figure 3: The verification of NTUPZE. Voltage gain and efficiency are as functions of load resistance.

Figure 4: The convergence behaviors of the GA process of (a) the single-output PT and (b) the dual-output PT.

Figure 5: The gain and the efficiency vs. the output section (D) for the single-output PT.

| Parameters                                | Туре             | Single-<br>output PT | Dual-<br>output PT |

|-------------------------------------------|------------------|----------------------|--------------------|

| GA<br>Parameters                          | Chromosome #     | 40                   |                    |

|                                           | Generation #     | 40                   |                    |

|                                           | Mutation ratio   | 0.08                 |                    |

|                                           | Pick ratio       | 0.8                  |                    |

|                                           | Opt. Cost value  | 0.081                | 0.089              |

| Dimensions & Performances of Opt. Devices | Device radius    | 12.7 mm              | 19.7 mm            |

|                                           | Output Sec. rad. | 12.7 mm              | 12.4 mm            |

|                                           | Electrode radius | 4.11 mm              | 5.4 mm             |

|                                           | Thickness        | 1 mm                 | 1 mm               |

|                                           | Load Impedance   | 100 k ohm            |                    |

|                                           | Max efficiency   | 91.9%                | 91.1%              |

|                                           | Optimized gain   | 53.8                 | 57.7               |

Table 1: The GA parameters and the optimized results of the two disk-type PT cases

Figure 6: The deformed shape of the optimal design operating at resonance frequency for (a) the single-output case and (b) the dual-output case.

# 3.2 Dual-output PT with Crescent-Shaped Electrodes

The schematic of the PT with dual outputs is shown in Figure 1. The poling directions and the design of the disktype dual-output PT with crescent-shaped electrodes are similar to those of the single-output PT. In order to ensure the performances for both outputs are the same, a symmetric design is employed. In this case, there are four design parameters: the radius (D) of the two output sections, the radius (C) of the two output electrodes, the radius (M) of the device structure and the thickness (M) of the device. Again, the design goal is to maximize the efficiency for both outputs under the constraint that the voltage gain has to be greater than 50 in order to meet the requirement of igniting CCFL.

The material properties are the same as those of the single-output PT. The resistive loads connected on the two

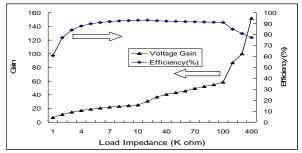

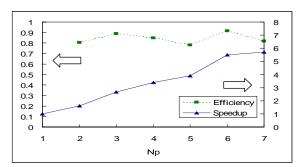

output electrodes are  $100 k\Omega$ . The design space is as follows: the output radius is from 4 mm to 12 mm, the electrode radius is from 2 mm to 8 mm, the device radius is from 10 mm to 20 mm, the device thickness is from 1 mm to 3 mm. The resolution of the genes is 5 bits. Figure 4(b) shows the GA convergence behavior of this case. The optimized D, C, M, and H are 12.40 mm, 5.43 mm, 19.69 mm, and 1 mm, respectively. The corresponding voltage gains for both outputs are 57.5. Also, the corresponding efficiencies for both outputs are 91.1%. Table 1 summarizes these results. The characteristics of the optimal PT with different loading  $R_L$  are shown in Figure 7. Obviously, the gains increase with the load impedance. However, the efficiency is less than 90% as the load impedance is larger than  $100 \, k\Omega$ . Figure 6(b) shows the deformed shape of the optimal design operating at resonance frequency. Figure 8 shows the benchmarks of the parallelized computations for the dual-output case. There are eight computers in our PC cluster. One of the computers serves as the manager. Each node is equipped with an Intel Pentium 4 CPU 3.0 GHz and 1GB memory. These nodes are interconnected through a Gigabit Ethernet network. The speedup and the efficiency for the parallel computation are defined as Equations (4) and (5). T(1) and  $T(N_P)$  represent the execution time for 1 and  $N_p$  nodes, respectively.

$$Speedup = \frac{T(1)}{T(N_p)} \tag{4}$$

$$E_{parallel} = \frac{Speedup}{N_p} \times 100\%$$

(5)

As shown in Figure 8, the more computers are used, the less computation time is needed. However, the computation efficiency ( $E_{parallel}$ ) might not be proportional to the number of computer nodes (the workers) when more PC nodes are used. It is because the total number of chromosomes which actually require the NTUPZE computations might be fewer than the computer nodes when the GA process is approaching convergence.

Figure 7: Load resistance dependence of the voltage gains and the efficiencies of a dual output PT.

Figure 8: The benchmarks of the parallelized GA computations for the dual-output case.

# 4 CONCLUSIONS

In this work, the optimizations of two disk-type piezoelectric transformers (PTs) using genetic algorithm is presented. One of the PTs has single output electrode with crescent-shaped input electrodes, and the other disk-type PT has dual output electrodes with elliptically-shaped output electrodes. The dimensions of the output sections, the output electrode, and the device structure are the design parameters. The maximum efficiency and the required voltage gain to ignite CCFL are the design goals and the design constraint, respectively. The simulations were preformed by using the finite element solver, NTUPZE. The results were also verified with measured data. A parallel computation platform using a PC cluster is also implemented in order to speed up computational time. Benchmark results of the parallelized genetic algorithm

process are also presented. The characteristics of the optimal designs with different loads are also estimated by the NTUPZE. The voltage gain of the optimal PT with single output electrode is above 50, which is sufficient to ignite CCFLs. The efficiency of the optimal PT with single output electrode is above 90%. The optimized dual-output PT, which can ignite 2 CCFLs simultaneously, also gives sufficient voltage gains of greater than 57 for both output electrodes.

### **ACKNOWLEDGEMENT**

This project is supported by the National Science Council, Taiwan (Contract No: 95-2622-E-002-003)

#### REFERENCES

- [1] C. A. Rosen, "Solid State Magnetic and Dielectric Devices," John Wiley & Sons, New York, 1<sup>st</sup> ed., Chap. 5, pp.170, 1959.

- [2] H. W. Joo, C. H. Lee, J. S. Rho and H. K. Jung, "Identification of Material Constants for Piezoelectric Transformers by Three-Dimensional, Finite-Element Method and a Design-Sensitivity Method," IEEE Transactions On Ultrasonics, Ferroelectrics, And Frequency Control, Vol. 50, No. 8, August 2003.

- [3] J. Weisman, "Introduction to Optimization Theory," Prentice-Hall, Inc., 1973.

- [4] E. M. Baker, W. Huang and D. Y. Chen, "Radial mode piezoelectric transformer design for fluorescent lamp ballast applications," IEEE Transactions On Power Electronics, Vol. 20, No. 5, September 2005.

- [5] J. M. Seo, H. W. Joo and H. K. Jung, "Optimal design of piezoelectric transformer for high efficiency and high power density," Sensors and Actuators A 121 (2005) 520-526.

- [6] Y. M. Chen, "The Modeling and Simulation of the Piezoelectric Transformers by the finite element method", M. S. Dissertation, Department of Mechanical Engineering, National Taiwan University, 2004.

- [7] B. Koc, Y. Gao and K. Uchino, "Design of a Circular Piezoelectric Transformer with Crescent-Shaped Input Electrodes," Jpn. J. Appl. Phys. Vol. 42 pp.509-514, 2003.

- [8] M. J. Quinn, "Parallel Programming in C with MPI and OpenMP," McGraw-Hill, 2003.

### APPENDIX A

$$\rho = 7500 \frac{kg}{m^3}$$

$$[C] = \begin{bmatrix} 140 \times 10^{10} & 7.1 \times 10^{10} & 7.3 \times 10^{10} & 0 & 0 & 0 \\ 7.1 \times 10^{10} & 140 \times 10^{10} & 7.3 \times 10^{10} & 0 & 0 & 0 \\ 7.3 \times 10^{10} & 7.3 \times 10^{10} & 11.5 \times 10^{10} & 0 & 0 & 0 \\ 0 & 0 & 0 & 2.6 \times 10^{10} & 0 & 0 \\ 0 & 0 & 0 & 0 & 2.6 \times 10^{10} & 0 \\ 0 & 0 & 0 & 0 & 0 & 3.0 \times 10^{10} \end{bmatrix}$$

$$[e] = \begin{bmatrix} 0 & 0 & 0 & 0 & 10.5 & 0 \\ 0 & 0 & 0 & 10.5 & 0 & 0 \\ 0 & 0 & 0 & 10.5 & 0 & 0 \\ -4.1 & -4.1 & 14.1 & 0 & 0 & 0 \end{bmatrix} C_{m^2}$$

$$[\varepsilon] = \begin{bmatrix} 7.124 \times 10^{-9} & 0 & 0 \\ 0 & 7.124 \times 10^{-9} & 0 \\ 0 & 0 & 5.841 \times 10^{-9} \end{bmatrix} F_{m}$$