## **CMOS Compatibility of Carbon Nanotubes on SOI Devices**

M.S. Haque<sup>1</sup>, S. P.Oei<sup>1</sup>, K.B.K.Teo<sup>1</sup>, F. Udrea<sup>1</sup>, J.W. Gardner<sup>1,2</sup>, W. I. Milne<sup>1</sup>

1. Department of Engineering, University of Cambridge, Trumpington Street, Cambridge CB2 1PZ, UK Email:msh42@cam.ac.uk, <u>fu@eng.cam.ac.uk</u>

Tel: +44(0)1223 748311, Fax:+ 44 (0)1223 748348

2. School of Engineering, Warwick University, Coventry CV4 7AL, UK

## **ABSTRACT**

This paper reports for the first time PECVD and CVD growth of Multiwalled Carbon Nanotubes (MWNTs) both aligned and non aligned on high temperature, partially depleted CMOS SOI substrates. We also report for the first time the growth of Carbon Nanotubes on SOI ultra-thin membranes with the use of different catalysts (Fe, Ni) and optimized for vertically aligned and non aligned growth. The SOI substrates, featuring CMOS devices and circuits, were subsequently tested to check the electrical performance after the high temperature growth. These particular wafers also contained some advanced high power devices and their functionality has been found to be virtually unchanged after CNT growth which proves that the CNT growth is fully compatible with CMOS SOI and the membrane technologies.

*Keywords*: MWCNTs, Silicon on Insulator, MOSFET, CVD, PECVD.

## 1 INTRODUCTION

Recently Carbon Nanotubes [1,2,3] have been extensively studied due to their unique properties. This technologically important material can be used for potential applications such as chemical sensors, nano electronic devices, field emission displays etc. On the other hand SOI technology has also been investigated for better performance in CMOS devices. The integration of the two technologies is of high interest both from a device/application perspective and from a technology perspective. The SOI CMOS is the only CMOS technology with high operating temperature capability (typically 225-250 °C, but in some cases even higher) and, when coupled with high temperature metallization can also allow post CMOS processing well in excess of 500 °C (the limit for standard CMOS). Thus the SOI technology is an ideal platform for CNT-CMOS integration.

Our experiments indicated that Carbon Nanotubes can be grown on SOI membranes using PECVD for aligned growth. For CVD growth, temperatures in excess of 785°C are required because of the lack of plasma that normally accelerates the growth of CNTs. On the other hand, for PECVD, temperatures below 650°C can be used as the plasma provides the activation energy. Nevertheless the

arcing caused by plasma can damage the devices and thus lowering the source voltage below 450V after the first few minutes is advisable. For growth of non aligned, spaghetti type CNTs, the optimum time was 15 minutes.

### 2 GROWTH PROCESS DETAILS

Carbon Nanotubes can be obtained using several techniques such as using high pressure arcs, laser ablation, and high pressure chemical vapour deposition [8-13]. Using Plasma Enhanced Chemical Vapour Deposition (PECVD) and CVD the MWNTs were grown on SOI membranes directly coated with a suitable transition metal catalyst. There were certain essential parameters when growing the nanotubes: (i) the feed gas (ii) the nature of the catalyst [4,5] (iii) the substrate temperature (iv) barrier layers used for growth. PECVD has been chosen for the growth of the carbon nanotubes because the technique is most efficient and reliable to grow aligned nanotubes. CVD and other techniques without plasma would grow the tubes on the membranes which would be entangled with each other i.e. the nanotubes would not be aligned. The reason for having aligned nanotubes is that it has very high aspect ratio which can be controlled and is repeatable. Spaghetti like nanotubes were grown on the membranes for gas sensing applications which allows better conductive path than the aligned tubes which are not entangled.

A graphite stage was connected to copper rods for heating up the substrates to the required temperature measured by a thermocouple. The sample was exposed to gases (NH<sub>3</sub>, C<sub>2</sub>H<sub>2</sub>, H<sub>2</sub>) using a shower head. The Carbon Nanotubes were grown on a resistively heated graphite substrate using a direct current (dc) glow discharge CVD system. The catalyst layers iron or nickel up to 2nm was deposited onto the SOI wafers using a magnetron sputter deposition system or thermal evaporation. After depositing the catalyst layer, the substrates were transferred to the growth chamber. The bell jar chamber was pumped down to a base pressure of 2 x 10<sup>-1</sup>mbar using a rotary pump. High purity nitrogen was then introduced via a leak valve and the substrate was heated to a temperature of 650°C (optimised temperature) and held at this temperature for a few minutes. The catalyst island form during this stage and after this treatment step ammonia (NH<sub>3</sub>) was introduced immediately which was maintained by mass flow controllers at 120 sccm, achieving a pressure of 4.0 mbar.

The bias voltage (Vb) was increased to -620 V (optimised voltage) and the acetylene ( $C_2H_2$ ) feed gas was introduced within a few seconds using a separate mass flow controller at 30sccm. The depositions were carried out for

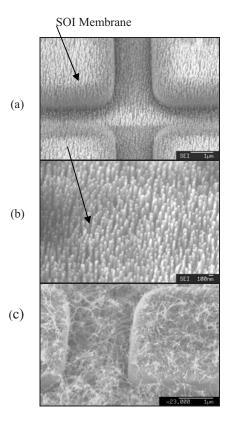

Figure 1: (a) Vertically aligned CNT on SOI membranes grown at 650  $^{\circ}$ C (b) Carbon Nanotubes on the membranes with diameter ranging from 60 nm - 160 nm. (c) Spaghetti like MWCNT on SOI membranes - diameter ranging from approximately 40 nm - 130 nm grown at 780  $^{\circ}$ C.

20 minutes in a stable discharge. The nanotubes are actually grown by the decomposition of the carbonaceous gas acetylene i.e.  $C_2H_2$  on the surface of the catalyst particles. Carbon from acetylene dissolves and diffuses through the catalysts and exits to form the nanotube. The role of the NH<sub>3</sub> is to etch by-products such as amorphous carbon. The nanotubes were then characterized using scanning electron microscopy (SEM) and Raman spectroscopy.

The growth results showed that the catalyst thickness or choice of catalyst (Fe or Ni) is important in controlling the nanotube diameter, length, density on the thin membranes, and their alignment is controlled by the electric field. Deposition temperature and plasma characteristics were also important for the growth of uniform, well-aligned nanotubes with few defects.

CVD on the other hand requires higher temperature for growth (750-785  $^{\circ}\text{C}$ ) because the plasma which provides the activation energy is not applicable in the process. The SOI membranes with different devices were heated to 750  $^{\circ}\text{C}$ . The spaghetti like carbon nanotubes deposition was performed with fixed gas flow rate, pressure and temperature of 200 sccm of NH $_3$ , 40 sccm of  $C_2H_2$ , 5.8mbar and 785  $^{\circ}\text{C}$ . The deposition produced wires which were few microns long. Figure 3 is showing the HRSEM of the spaghetti like carbon nanotubes on the SOI membranes and different devices [6] like n and p channel MOSFET, IGBTs, and tungsten heaters.

#### 3 RESULTS

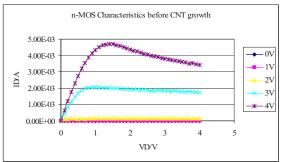

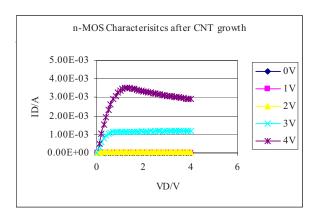

## 3.1 MOSFET Characteristic before and after CNT growth

MOSFETs on SOI membranes have been tested before and after the growth of carbon nanotubes for electrical and thermal functionality. SOI micro-heater MOSFETs embedded in thin membranes have also been extensively tested. While the devices placed on solid substrates have changed insignificantly, we observe a change in the threshold voltage on the FET devices placed within the membrane. This may be due to charge induced during the plasma process and also possibly the change in the mechanical stress within the membrane. Later experiments have verified that it is due to the probe and the pad series resistance. It should be noted that the membrane FET devices feature no passivation on the back-surface and therefore they can be more easily affected by plasma charging. The micro-hotplates feature top interdigitated electrodes made of the upper CMOS metal layer, onto which the CNTs are grown. It is worth noting that standard bulk CMOS technology based on Aluminum metallization is not compatible with the post-CMOS growth of CNTs due to the low melting point of Al. In contrast, high temperature SOI using Tungsten as an interconnect metal is well suited. The electro-thermo-mechanical properties offered by SOI also makes it unique as a platform technology for smart integration of CNTs in SOI sensors such as chemical sensors. This type of architecture can be used for resistive gas-sensors.

Figure 2a: IV MOSFET Characteristics before CNT growth.

Figure 2b: IV Characteristic of MOSFET after CNT growth.

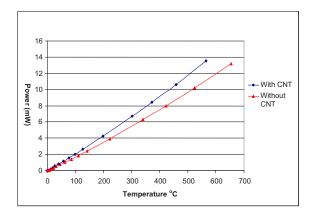

# 3.2 Tungsten heater characteristic before and after CNT growth

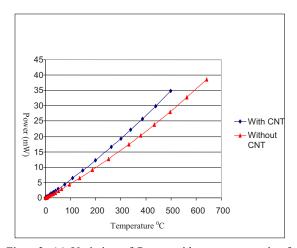

Novel tungsten micro heaters have been designed for resistive gas sensor and calorimetric devices. Tungsten which is mechanically strong and reliable at higher temperatures has a reasonably high resistivity and stable operation at high temperatures which makes it ideal as a material for microheaters. At the same time, the tungsten resistivity is low enough to be used for interconnects in CMOS circuits. Carbon Nanotubes were grown above tungsten heaters and tested for variation of power dissipation with temperature rise. Figure 3a shows the plot for the small tungsten heater and at a temperature of around 500 °C the difference of power dissipation with CNT films on the chip was about 16%. For the larger heater (Figure 3b) the dissipation was about 17%. The difference in power dissipation is due to the high thermal conductivity of carbon nanotubes which contributes to lateral thermal dissipation from the heater to the substrate. The increase surface area of nanotubes also tends to slightly increase the convection. This is more visible at temperatures in excess of 300 °C.

Figure 3: (a) Variation of Power with temperature rise for small tungsten heaters (b) Variation of Power with temperature rise for large tungsten heaters

## 4 CONCLUSION

In this paper we have demonstrated for the first time the growth of various CNTs on SOI CMOS substrates and on SOI-based membranes. These substrates contained fully processed, advanced CMOS and bipolar devices and circuits using Tungsten metallization. We have concluded that the basic functionality is unchanged after high temperature growth of CNTs. The electro-thermal behavior of the membranes is slightly changed as the CNTs add a thermal conductive/convective path, this can be minimized by selective growth of CNTS only on the centre of the membranes. The CNT growth temperature proposed in this paper (i.e. 650 °C) could be lowered for better performance and higher yield. This may avoid formation of dislocations or in the worst case, cracking or of the actual substrate. This is particularly the case when the growth was done on the thin SOI membranes. In general, the devices offered good thermal stability and uniformity before and after the growth of Carbon Nanotubes.

#### 5 ACKNOWLEDMENT

F. Udrea acknowledges the award of a Leverhulme prize. S. Haque acknowledges the support of Charles Wallace and Cambridge Commonwealth Trusts. This research has been party sponsored by the Electronics and Telecommunications Research Institute (ETRI), Korea.

## REFERENCES

[1] S. Iijima, Nature, 354, 56, 1991.

[2] H.E. Kroto, J.R Heath, S.C. O'Brien, R.F. Curl, R.E. Smalley, Nature, 318, 162,1985.

[3] S. Iijima, T. Ichihashi, Nature, 363, 603, 1993.

- [4] K.B.K Teo, M Chhowallla, G.A.J Amaratunga and W.I.Milne, Applied Physics Letters, Vol 79, No.10 3 September 2001.

- [5] M Chhowallla, K.B.K Teo, C.Ducati, Journal of Applied Physics, Vol.90 No.10, 15 November 2001.[6] F. Udrea, T. Trajkovic and G. A. J. Amaratunga,

- [6] F. Udrea, T. Trajkovic and G. A. J. Amaratunga, "Membrane High Voltage Devices A Milestone Concept in Power ICs", IEEE proceedings 2001.

- [7] Lu, Chih-Cheng, Udrea, Florin; Gardner, Julian W, Proc. SPIE Vol. 4408, p. 86-95, Design, Test, Integration, and Packaging of EMS/MOEMS 2001.

- [8] Julian W. Gardner, Florin Udrea, W.I. Milne, SPIE Proceedings pp.104-112, 1999.

- [9] C. Hu et al, Jpn. J. Appl. Phys., vol. 33, pp. 365–369, Jan. 1994.