# Effect of Etchant Composition and Equipment Parameters on Silicon Etch Rate

D. Yellowaga\*, J. Starzynski\*\*, B. Palmer\*, J. McFarland\* and S. Drews\*\*\*

\*Honeywell Electronic Chemicals 6760 W. Chicago St, Chandler, AZ, USA 85226 \*\*Honeywell Electronic Chemicals 12001 State Highway 55, Plymouth, MN, USA \*\*\*SEZ America 4829 S. 38<sup>th</sup> St. Phoenix, AZ, 85040

### **ABSTRACT**

The drive for faster and smaller electronics has created an increased need for denser die stacking and smaller die packaging. Thinner substrates are in paradox with the other trend in advanced IC technologies: increased wafer diameter. In order to meet the requirements for packaging, stacking, mechanical reliability and faster switching speeds, the thickness of the wafer must be reduced before the device is diced for packaging. Currently, approximately 25% of all finished devices require thickness reduction, and that amount is expected to approach 80% within 5 years. Physical grinding of the wafers introduces damage in the back surface of the silicon that leads to early failures once the device has been packaged. It has been shown that by removing as little as 8u of damaged silicon leads to an 80% reduction in the amount of stress on the wafer [1]. In this paper, factors that affect the etch rate and uniformity of wafer thinning etchants as a function of equipment parameters and acid composition were determined.

Keywords: wafer thinning, backside etch, grinding, stress relief

#### 1 INTRODUCTION

Wet etch methods for reducing the thickness of a silicon wafer have been gaining popularity over traditional thinning methods of physical grinding or plasma treatment. wafers is quick, offers yield Wet etch thinning of improvements over grinding methods, and allows more expensive plasma equipment to be freed up for other processes. Wet etch wafer thinning products on the market today are typically an acidic mixture of 3 or 4 components, comprising chelating acids, oxidizing acids and diluent acids. Diluent acids are chosen for water absorption or viscosity properties, and their ability to control dissociation of other acids in the mixture [2,3]. Adding acids of increased viscosity also reduces the surface roughness resulting from the etch [2]. Etchants are usually applied to the back side of a wafer in a single wafer spray tool before the wafer is diced for packaging. Etchant compositions can be modified to achieve different etch rates and surface textures for silicon. In the case of a bulk silicon etch, acid compositions are chosen to have a high etch rate, but minimal dishing and wafer bow effects when applied in the toolset. Silicon polish etchants have compositions chosen to increase the overall viscosity of solution, which acts to delineate cracks formed during physical grinding of the silicon surface. Texture etchants are designed to maximize surface roughness of the wafer surface, to increase adhesion for metal layers applied to the back of the wafer.

Equipment technology available for the application of wet chemical etchants for wafer thinning is mature and robust, but one of the obstacles to wet etch wafer thinning becoming more widely accepted is the difficulty in controlling the manufacturing process for the etchants. Blending of the acids typically contained in these mixtures can be highly exothermic, and more volatile components in these mixtures can be lost. This creates very large lot to lot inconsistencies of product, which leads to changes in etch rate and uniformity when applied to the wafer [4].

## 2 EXPERIMENTAL

Variations in composition of Honeywell Wafer Thinning Products Bulk Silicon Etchant, Silicon Polish Etchant 1, Silicon Polish Etchant 2, and Silicon Texture Etch were tested on <100> silicon. Etch rates for <100> silicon were measured according to the standard method DIN 50453, which is a gravimetric method whereby silicon coupons of known dimensions are weighed pre and post etchant application. Variations in etchant compositions to be tested were determined using an extreme vertices mixture design of experiments using Minitab version 14.12. Etch rate results were analyzed using stepwise regression. For etch rate and uniformity testing for Honeywell Wafer Thinning Products, etchants were applied to 8" <100> silicon wafers in a SEZ 203, which is a single wafer spin processor for advanced frontside and backside etching. stripping, cleaning, wafer reclaim and film removal applications. Equipment parameters were varied as part of a Box-Behnken surface response design, and resulting etch rates and etch uniformities were determined using a FSM 413C optical wafer thickness mapper. Surface roughness after etch was measured using a KLA Tencor P2 long scan profiler.

# 3 RESULTS

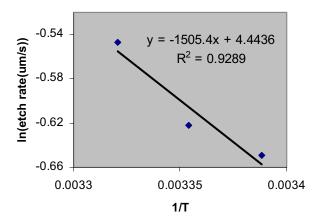

For the Bulk Silicon Etchant, the amount of the 4 different components were varied by approximately 6 to 8 percent by volume, which gave percent by weight variations of 3 to 7 %, depending on the acid. The resulting formulations had etch rates ranging from just under 100 µm/min to over 140 µm/min (see figures 1 to 6). Etch rates obtained in a beaker are much higher than would be obtained in a full wafer tool, as the toolsets apply active cooling to the opposite side of the wafer during the etch process, and the etch is very exothermic. It was found that the etch rates were heavily dependent on all of the acids present in the mixture. There was also found to be a positive correlation between the etch rate and water content by weight of the bulk silicon etchant. Increasing water content will increase the degree of dissolution of the acids in the formulation, which accounts for the increase in etch rate [3]. When the Bulk Silicon Etchant was applied in the SEZ 203 spin processor, it was possible to obtain etch rates between 26 and 40 µm/min on an 8" wafer by simply adjusting the equipment parameters. Etch uniformity was excellent for almost all equipment parameters tested, showing that there was a broad process window for the Bulk Silicon Etchant. The etch rate of silicon in the Bulk Silicon Etchant is first order as is shows Arrhenius behavior as illustrated by a plot of the natural log of the etch rate versus the inverse of the temperature in Kelvins.

#### **Arrhenius Plot for Bulk Silicon Etchant**

Figure 1: Arrhenius behavior of Bulk Silicon Etchant.

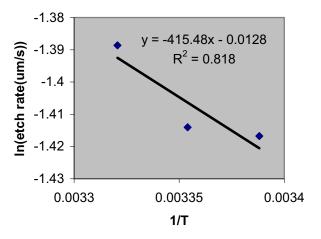

For Silicon Polish Etchant 1, the amount of the 4 different components were varied by approximately 5 to 8 percent by volume, which gave percent by weight variations of 2 to 5 %, depending on the acid. Etch rates in the DIN 50453 testing ranged from 3 to 6  $\mu$ m/min. When the Silicon Polish Etchant 1 was applied in the SEZ 203

spin processor, it was possible to obtain etch rates between 12 and 17  $\mu$ m/min. Once again, etch uniformity was excellent for a wide range of equipment parameters tested. The etch rate of silicon in the Silicon Polish Etchant 1 also showed Arrhenius behavior.

#### **Arrhenius Plot for Silicon Polish Etch 1**

Figure 2: Arrhenius behavior of Silicon Polish Etchant 1

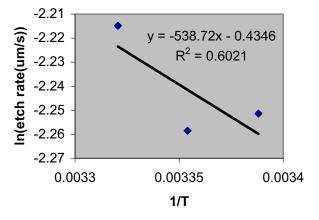

In the case of Silicon Polish Etchant 2, the amount of the 4 different components were varied by approximately 5 to 10 percent by volume, which gave percent by weight variations of 2 to 6 %, depending on the acid. Resulting etch rates are in the range of 0.5 to 3  $\mu m/min$  in the DIN test. When the Silicon Polish Etchant 2 was applied in the SEZ 203 spin processor, it was possible to obtain etch rates between 5 and 8  $\mu m/min$ . Etch uniformity was very good for a wide range of equipment parameters tested. The etch rate of silicon in the Silicon Polish Etchant 2 did not have as good of fit in the Arrhenius plot, suggesting that second order effects on etch rate may be occurring.

#### **Arrhenius Plot For Silicon Polish Etch 2**

Figure 3: Arrhenius behavior of Silicon Polish Etchant 2

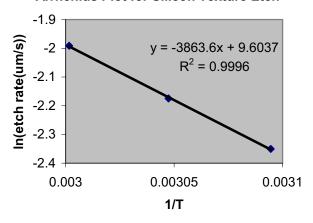

For Silicon Texture Etchant, measurements for composition variations and etch rate and surface roughness were all measured on  $8^{\prime\prime}$  <100> wafers processed in the SEZ 203. Etch rates between 4 and 8  $\mu m/min$  were achieved through equipment parameter manipulation. Surface roughnesses of up to 2400  $R_a$  were also possible through variations in equipment settings. The etch rate of silicon in the Silicon Texture Etchant showed excellent Arrhenius behavior.

#### **Arrhenius Plot for Silicon Texture Etch**

Figure 4: Arrhenius behavior of Silicon Texture Etchant

#### 4 SUMMARY

As shown from the experimental results, changes of a few percent in acid composition can lead to changes in the etch rates that could create issues in a manufacturing environment. Honeywell Wafer Thinning Products are produced under strict manufacturing controls, and show excellent batch to batch uniformity amongst constituents. All of the etchants except for the Silicon Polish Etchant 2 showed Arrhenius behavior, which means the etch rate mechanism is first order. This is desirable as first order mechanisms are more easily predicted and are easier to control. It was also shown that etch rates and surface finish could be easily controlled through equipment parameter settings. Overall, Honeywell Wafer Thinning Products showed excellent uniformity over a wide range of equipment parameters, proving that there are wide process windows for these products.

#### 5 ACKNOWLEDGEMENTS

The authors would like to thank Aaron Bicknell, Applications Engineer, and Gale Hansen, Metrology Engineer from the SEZ America Research Lab in Phoenix, Arizona for their invaluable assistance in this project.

# **REFERENCES**

- [1] C. McHatton and C. M. Gumbert, *Solid State Technology*, **41**, 11, (1998).

- [2] M. S. Kulkarni, H. F. Erk, *J. Electrochem. Soc.* **147**, 176 (2000).

- [3] H. Robbins, B. Schwartz, *J. Electrochem. Soc.* **107**, 108 (1960).

- [4] W. Seivert, K. Zimmermann, J. A. McFarland, M. A. Dodd, United States Patent Application Publication US20030230548.