### Recent enhancements of MOS Model 11

R. van Langevelde, A.J. Scholten and D.B.M. Klaassen

Philips Research Laboratories

Prof. Holstlaan 4, 5656 AA Eindhoven, The Netherlands, ronald.van.langevelde@philips.com

#### ABSTRACT

MOS Model 11 (MM11) is a surface-potential-based compact MOSFET model, which was introduced in 2001 (level 1100). An update of MM11, level 1101, was introduced in 2002. At the moment a second update of MM11, level 1102, has been completed and is under test. It includes: i) an iterative solution of the surface potential; ii) an improved description of the velocity saturation yielding a better modelling of the transconductance in saturation; and iii) a better description of noise, especially the induced gate current noise. In this paper we describe these improvements and show the resulting improved modelling of transistor performance.

Keywords: MOS Model 11, compact MOSFET modelling, surface potential, thermal noise, induced gate noise

#### 1 INTRODUCTION

There are three categories of compact MOS models: i) threshold-voltage-based models, ii) inversion-charge-based models, and iii) surface-potential-based models. Since the latter category of models give a physics-based and accurate description in all operation regions, experts judge them to be the most successful in describing deep-submicron CMOS technologies for demanding analogue and RF applications [1]. As a result, most new MOS models in the public domain are surface-potential-based [1]-[3].

MOS Model 11 (MM11) is a surface-potential-based compact MOSFET model, which has been developed with special emphasis on the preservation of source-drain symmetry and on an accurate description of distortion behaviour. MM11 was introduced in 2001 (level 1100, indicated by MM1100) and contains all major physical effects such as poly-depletion for the gate, gate tunnelling current and quantum-mechanical quantisation effects. During 2002, an update of MM11, level 1101 (MM1101), has been introduced [4]. The main enhancements of MM1101 over MM1100 are: i) the modelling of gate-induced drain leakage, ii) a rigorous separation of geometrical and temperature scaling rules for the model parameters, and iii) a separate set of geometrical scaling rules for the model parameters, especially designed

for binning. In MM1101, there is a choice to use the physics-based geometrical scaling rules **or** the binning geometrical scaling rules for the model parameters.

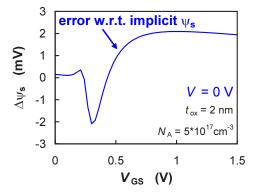

Figure 1: Absolute error in the approximate surface potential (as used in MM1101) with respect to the exact solution of the implicit equation.

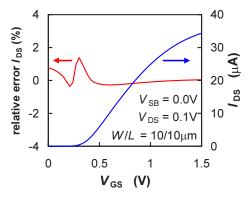

Figure 2: Relative error in the current using the approximated and exact solution of the surface potential corresponding to Fig. 1.

As mentioned before, surface-potential-based models give a physics-based and accurate description in all operation regions. The main drawback of these models, however, is the fact that only an implicit equation for the surface potential can be derived. The solution to this implicit equation can be either approximated an-

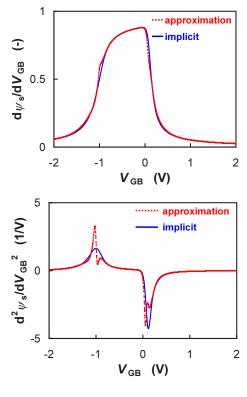

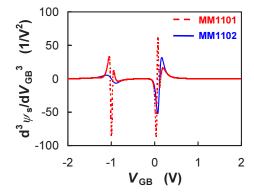

Figure 3: First-order derivative (top) and second-order derivative (bottom) of the surface potential  $\psi_s$  with respect to the gate-bulk voltage. Both the result of the implicit relation for surface potential (solid line) and the explicit approximation for surface potential as used in MM1101 (dashed line) are shown.

alytically or found exactly by iteration. MM1101 uses an analytical approximated solution of the surface potential, which is computationally very efficient [5]. This approximated solution shows only small deviations with respect to the exact solution of the implicit equation for the surface potential, see Figure 1. The error in the current caused by this deviation is negligible, see Figure 2. When, however, the first-order and, especially, the second-order derivatives of the surface potential with respect to the gate-bulk voltage are inspected, larger deviations show up, see Figure 3. This leads to an error in the input capacitance  $C_{\rm GG}$ , and may be a problem when modelling the distortion of MOS varactors.

More accurate analytical approximations for the surface potential have been published [1], [6]. These approximations are, however, also computationally inefficient compared to our approximation. Therefore we have adopted an iterative solution of the surface potential in MM1102. In addition to this we have also improved the description of the velocity saturation and added a better description of noise, especially the induced gate current noise. These three improvements

will be described in the next Sections.

## 2 ITERATIVE SOLUTION OF THE SURFACE POTENTIAL

The surface potential  $\psi_s$  is defined as the electrostatic potential at the gate oxide/substrate interface with respect to the neutral bulk. For an n-type MOSFET with uniform substrate doping  $N_{\rm A}$  and oxide capacitance  $C_{\rm ox}$ ,  $\psi_{\rm s}$  can be calculated from the following implicit relation [7]:

$$\left(\frac{V_{\rm GB}^* - \psi_{\rm p} - \psi_{\rm s}}{k_0}\right)^2 = \psi_{\rm s} + \phi_{\rm T} \cdot \left[\exp\left(-\frac{\psi_{\rm s}}{\phi_{\rm T}}\right) - 1\right] (1)

+ \phi_{\rm T} \cdot \exp\left(-\frac{\phi_{\rm B} + V}{\phi_{\rm T}}\right) \cdot \left[\exp\left(\frac{\psi_{\rm s}}{\phi_{\rm T}}\right) - \frac{\psi_{\rm s}}{\phi_{\rm T}} - 1\right]$$

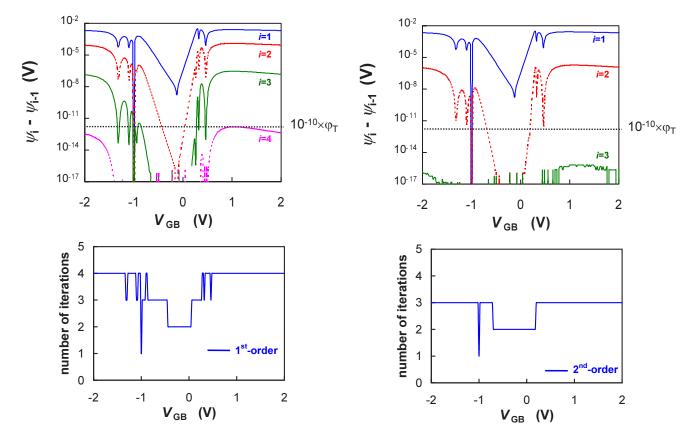

where  $V_{\rm GB}^*$  is the effective gate bias ( $V_{\rm GB}^*=V_{\rm GB}-V_{\rm FB}$ ),  $V_{\rm FB}$  is the flat-band voltage,  $\psi_{\rm p}$  is the potential drop in the polysilicon gate due to poly-depletion,  $k_0$  is the body factor of the silicon substrate ( $k_0$  =  $\sqrt{2 \cdot q \cdot \epsilon_{\rm Si} \cdot N_{\rm A}}/C_{\rm ox}$ ,  $\phi_{\rm T}$  is the thermal voltage ( $\phi_{\rm T} =$  $(k \cdot T/q)$ , and  $\phi_{\rm B}$  is twice the intrinsic Fermi-potential  $(\phi_{\rm B}=2\cdot\phi_{\rm T}\cdot\ln(N_{\rm A}/n_{\rm i}))$ . The above implicit relation for  $\psi_{\rm s}$  can be solved iteratively using the Newton-Raphson method [8]. Using a simple yet accurate zeroorder estimate of  $\psi_s$  and applying a first-order Newton-Raphson scheme to the implicit equation for the surface potential, a maximum of four iterations is needed to reach an accuracy of  $10^{-10} \cdot \phi_{\rm T}$ , where  $\phi_{\rm T}$  is the thermal voltage, see Figure 4. In an attempt to reduce the number of iterations needed to reach this accuracy, a second-order Newton-Raphson scheme has been investigated, see Figure 5. From this figure it can be seen that a maximum of only three iterations is needed to reach the same accuracy. Although the computational effort per iteration is slightly larger for the secondorder Newton-Raphson scheme compared to the firstorder Newton-Raphson scheme, the overall computation time is smaller for the second-order Newton-Raphson scheme. Hence we adopted the second-order Newton-Raphson scheme for MM1102. In Figure 6 the thirdorder derivative of the surface potential is shown as a function of gate-bulk voltage. From this figure it can be seen that with MM1102, the distortion modelling of varactors is greatly improved.

## 3 IMPROVED DESCRIPTION OF VELOCITY SATURATION

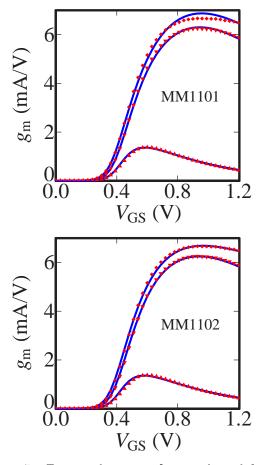

Although MM1101 gives an accurate description of the output  $I_{\rm D}$ - $V_{\rm DS}$  characteristics of short-channel devices, it nevertheless gives a slightly inaccurate description of transconductance  $g_{\rm m}$  in the saturation region, see Figure 7 (top). Close examination shows that this

Figure 4: **Top:** Absolute error in surface potential (as a function of gate-bulk voltage) between two successive iterations, where the number of  $1^{\rm st}$ -order Newton-Raphson iterations is indicated by i.

**Bottom:** Number of iterations that is needed to obtain an absolute error in surface potential between two successive iterations smaller than  $10^{-10}$  times the thermal voltage.

inaccuracy is caused by the velocity saturation expression used in MM1101. In MM1102, therefore, a more physical and accurate expression for velocity saturation is introduced, see Figure 7 (bottom). In this Section, we will briefly describe the derivation of this new velocity saturation expression.

With an increase in lateral electric field, carriers gain sufficient energy to be scattered by optical phonons, resulting in a decrease of mobility and eventually resulting in the saturation of drift velocity. This is often referred to as velocity saturation. For electrons, an accurate description of velocity saturation is given by [9]–[11]:

$$v = \frac{\mu \cdot \frac{\partial \psi_s}{\partial x}}{\sqrt{1 + \left(\frac{\mu}{v_{\text{sat}}} \cdot \frac{\partial \psi_s}{\partial x}\right)^2}}$$

(2)

Figure 5: **Top:** Absolute error in surface potential (as a function of gate-bulk voltage) between two successive iterations, where the number of  $2^{\text{nd}}$ -order Newton-Raphson iterations is indicated by i.

**Bottom:** Number of iterations that is needed to obtain an absolute error in surface potential between two successive iterations smaller than  $10^{-10}$  times the thermal voltage.

Figure 6: Third-order derivative of the surface potential with respect to the gate-bulk voltage for both level 1101 and level 1102 of MOS Model 11.

where  $\mu$  is the mobility and  $v_{\rm sat}$  is the saturation velocity. This expression can be incorporated in the drain-source channel current  $I_{\rm DS}$  by:

$$I_{\rm DS} = -\frac{\mu \cdot W \cdot Q_{\rm inv}^*}{\sqrt{1 + \left(\frac{\mu}{v_{\rm sat}} \cdot \frac{\partial \psi_{\rm s}}{\partial x}\right)^2}} \cdot \frac{\partial \psi_{\rm s}}{\partial x}$$

(3)

where  $Q_{\rm inv}$  is the inversion-layer charge density, and  $Q_{\rm inv}^*$  is given by:

$$Q_{\rm inv}^* = Q_{\rm inv} - \phi_{\rm T} \cdot \frac{\partial Q_{\rm inv}}{\partial \psi_{\rm s}} \tag{4}$$

The above differential equation (3) for  $I_{DS}$  is complicated, and is generally approximated by:

$$I_{\rm DS} = -\frac{\mu \cdot W}{G_{\rm vsat} \cdot L} \cdot \int_{\psi_{s_0}}^{\psi_{s_L}} Q_{\rm inv}^* \cdot d\psi_{\rm s}$$

(5)

where:

$$G_{\text{vsat}} = \frac{1}{L} \cdot \int_0^L \sqrt{1 + \left(\frac{\mu}{v_{\text{sat}}} \cdot \frac{\partial \psi_{\text{s}}}{\partial x}\right)^2} \cdot dx$$

(6)

A first-order approximation of the integral in (6) can be obtained by assuming that the lateral field  $-\partial \psi_{\rm s}/\partial x$  is constant along the channel and equal to  $\Delta \psi/L$  [10], [11]. In MM1101, a slightly better approximation of (6) is obtained by assuming that the lateral field  $-\partial \psi_{\rm s}/\partial x$  increases linearly along the channel from 0 at the source to  $2 \cdot \Delta \psi/L$  at the drain. In this case,  $G_{\rm vsat}$  is given by:

$$G_{\text{vsat}} = \frac{1}{2} \cdot \left[ \sqrt{1 + \Gamma^2} + \frac{\ln\left(\Gamma + \sqrt{1 + \Gamma^2}\right)}{\Gamma} \right]$$

(7)

where:

$$\Gamma = 2 \cdot \frac{\mu}{v_{\text{sat}}} \cdot \frac{\Delta \psi}{L} \tag{8}$$

As mentioned before, the above expression for velocity saturation results in an accurate description of the output  $I_{\rm D}$ - $V_{\rm DS}$  characteristics, but it nevertheless gives a slightly inaccurate description of transconductance  $g_{\rm m}$  in the saturation region, see Figure 7 (top).

In MM1102, velocity saturation is incorporated in a more physical and consequently more accurate way. The differential equation (3) for  $I_{\rm DS}$  is rewritten to:

$$I_{\rm DS} = \sqrt{\left(\mu \cdot W \cdot Q_{\rm inv}^*\right)^2 - \left(\frac{\mu}{v_{\rm sat}} \cdot I_{\rm DS}\right)^2} \cdot \frac{\partial \psi_{\rm s}}{\partial x} \quad (9)$$

Under the correct linearisation of  $Q_{\rm inv}^*$  with respect to  $\psi_s$ , the above expression can be integrated along the channel from source to drain, resulting in an implicit relation for  $I_{\rm DS}$ . Next, the resulting relation is approximated by a third-order Taylor expansion around

Figure 7: Transconductance of an n-channel MOS-FET with W/L= $10\mu$ m/ $0.13\mu$ m as a function of  $V_{\rm GS}$  at  $V_{\rm DS}=0.05,\,0.6,\,$  and  $1.2{\rm V}$  and  $V_{\rm SB}=0{\rm V}.$  Symbols indicate measurements; lines indicate model calculations with MM1101 (top), and MM1102 (bottom).

$I_{\rm DS}=0$ , which again leads to (5) where in this case  $G_{\rm vsat}$  is given by:

$$G_{\text{vsat}} = \frac{1}{2} \cdot \left[ 1 + \sqrt{1 + \frac{\Gamma^2}{2}} \right] \tag{10}$$

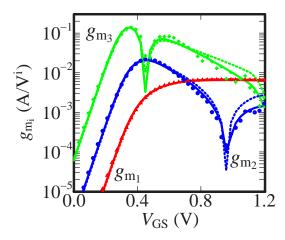

The above  $G_{\rm vsat}$ -expression is simpler than the MM1101-expression, nevertheless it gives a more accurate description of  $g_{\rm m}$  in the saturation region, see Figure 7 (bottom). As a result, MM1102 gives a more accurate description of distortion than MM1101, see Figure 8.

## 4 IMPROVED NOISE DESCRIPTION

#### 4.1 Introduction

Accurate compact modeling of noise is a prerequisite for RF CMOS circuit design. At the RF-frequencies used, besides the drain current thermal noise also the

Figure 8: First-  $(g_{\rm m_1})$ , second-  $(g_{\rm m_2})$ , and third-order  $(g_{\rm m_3})$  derivatives of the drain current with respect to the gate voltage as a function of  $V_{\rm GS}$  at  $V_{\rm DS}=1.2 \rm V$  for the device of Figure 7. Symbols indicate measurements; solid lines and dashed lines indicate model calculations with MM1102 and MM1101, respectively.

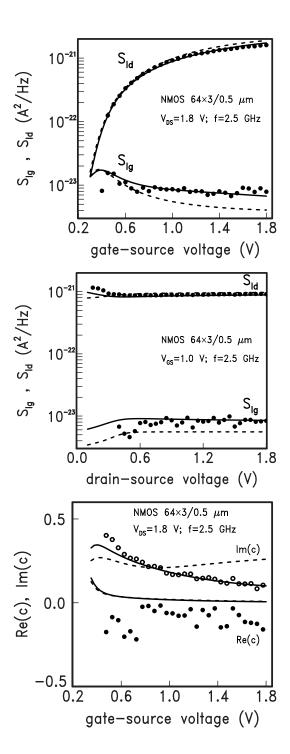

induced gate noise plays an important role. Over the years, several compact models for induced gate noise have been introduced [12]–[15]. Nevertheless, all of these models are based on the same Van der Ziel model [12], which is only valid in saturation. In addition, the Van der Ziel model is based on the Klaassen-Prins (KP) equation [16], which does not accurately account for velocity saturation [17]. As a result, the above models are inaccurate for short-channel devices, and more accurate modeling for induced gate noise is needed.

# 4.2 Correct Incorporation of Velocity Saturation in Noise Model

We use an improved KP-approach [18], where fluctuations in the velocity saturation term are also taken into account. Under the appropriate linearisations, the improved approach can be solved in the  $\psi_s$ -framework. The above noise model has been implemented in MM1102, where the impact of series resistance and short-channel effects (CLM, DIBL, etc.) have been incorporated as well. To be able to use the compact model for RF-applications, we furthermore extend the model with a gate resistor and a bulk resistance network.

#### 4.3 Experimental results

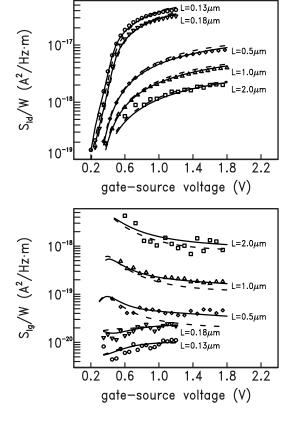

Noise measurements were performed on  $0.18\mu m$  and  $0.12\mu m$  RF CMOS technologies. Compact model parameters were extracted from DC-measurements, and gate and bulk resistance values were determined from Y-parameter measurements. In Figure 9, noise results are shown for a  $L=0.5\mu m$  MOSFET. MM1102 based on the improved KP-approach is in excellent agreement with the data without any additional noise parameter

Figure 9: Drain and gate current noise versus gate-source bias (top) and versus drain-source bias (middle), and correlation coefficient c versus gate-source bias (bottom) for an  $L=0.5\mu\mathrm{m}$  n-channel device in  $0.18\mu\mathrm{m}$  CMOS technology. Symbols denote measurements, dashed lines denote the Van der Ziel model, and solid lines denote MM1102 based on the improved KP-approach.

Figure 10: Drain current noise (top) and gate current noise (bottom) versus gate-source bias for n-channel devices with different channel length L. Symbols denote measurements, dashed lines denote Van der Ziel model, and solid lines denote MM1102 based on the improved KP-approach. ( $f=5\,\mathrm{GHz}$  and  $V_\mathrm{DS}=1.0\mathrm{V}$  for  $L\leq0.18\mu\mathrm{m}$ ,  $f=2.5\,\mathrm{GHz}$  and  $V_\mathrm{DS}=1.8\mathrm{V}$  for  $L\geq0.5\,\mu\mathrm{m}$ )

fitting. The Van der Ziel model, on the other hand, leads to a considerable error in the gate noise. The measured real part of c is slightly negative due to non-quasi-static effects, which are not taken into account in the modelling. Noise results for various channel lengths L are shown in Figure 10. MM1102 gives accurate results over all bias conditions and channel lengths. Using the Van der Ziel model leads to an underestimation of gate noise (up to 40%), particularly for intermediate L where velocity saturation is important. For short-channel devices, the differences between the two models are obscured due to the dominant impact of gate resistance (see e.g. [18]).

#### 5 SUMMARY

The newest update of MOS Model 11, level 1102 (MM1102), which is now under test, includes: i) an iterative solution of the surface potential; ii) an improved

description of the velocity saturation yielding a better modelling of the transconductance in saturation; and *iii*) a better description of noise, especially the induced gate current noise.

The iterative solution results in a more accurate description of surface potential. It has as additional advantage that new physical effects are easily added to the iterative scheme, while for an analytical approximation tedious algebra and often additional approximations for the individual physical effects have to be made. This also implies that: i) code maintenance is easier for an iterative solution scheme, and ii) the increase in simulation time is very limited. In fact, during test runs with MM1102 on circuits containing several hundreds of transistors an increase in simulation time of only 2 to 3 percent has been observed, while retaining the excellent convergence behaviour of MM1101.

More details and the code of MOS Model 11, level 1102, can be found on our website [19].

#### REFERENCES

- [1] G. Gildenblat *et al.*, *Proc. of IEEE CICC*, pp. 233-240, 2003.

- [2] R. van Langevelde et al., ESSDERC 2001, p. 81.

- [3] M. Miura-Mattausch et al., IEDM 2002, p. 109.

- [4] R. van Langevelde et al.,

"MOS Model 11, Level 1101," NL-UR 2002/802,

Philips Electronics N.V., 2002, see website of [19].

- [5] R. van Langevelde and F.M. Klaassen, Solid-State Electron., Vol. 44, pp. 409-418, 2000.

- [6] G. Gildenblat and T.-L. Chen, Solid-State Electron., Vol. 45, pp. 335-341, 2001.

- [7] C.C. McAndrew and J.J. Victory, *IEEE TED*, Vol. ED-49, No. 1, pp. 72-81, 2002.

- [8] A.R. Boothroyd et al., IEEE Trans. Computer-Aided Des., Vol. CAD-10, pp. 1512-1529, 1991.

- [9] D.L. Scharfetter and H.K. Gummel, IEEE TED, Vol. ED-16, No. 1, pp. 64-77, 1969.

- [10] R. van Langevelde and F.M. Klaassen, IEDM Tech. Dig., pp. 313-316, 1997.

- [11] K. Joardar et al., IEEE TED, 45, p. 134, 1998.

- [12] A. van der Ziel, Noise in Solid State Devices and Circuits, pp. 88-92, 1986.

- [13] BSIM4: www-device.eecs.berkeley.edu

- [14] C.H. Chen and M.J. Deen, Solid-State Elec., 42, pp. 2069-2081, 1998.

- $[15]\,$  G. Knoblinger,  $ESSDERC~2001,~{\rm pp.~331\text{--}334,\,2001}$

- [16] F.M. Klaassen and J. Prins, Philips Res. Repts., 22, pp. 505-514, 1967.

- [17] F.M. Klaassen, *IEEE TED*, **17**, pp. 858-862, 1971.

- [18] R. van Langevelde *et al.*, to be presented at IEDM, Washington D.C., 2003.

- [19] Documentation and source code of MOS Model 11, levels 1100, 1101 and 1102, can be found at: www.semiconductors.philips.com/Philips\_Models