# c-SI Wafer Development: A New Approach to Reduce Costs and Drive Efficiency

S. Zehavi'N. Reef, A. Blosse, D. Weiss, L. Hendler

\*Scifiniti Inc., 51 Daggett Dr. San Jose, CA 95134

#### ABSTRACT

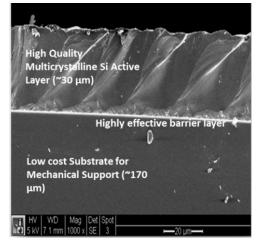

The main problems with the manufacturing processes used in crystalline silicon wafers include: (1) very wasteful process of casting and slicing yielding high kerf lost of about 50% of the silicon material; (2) the cost of equipment to produce thinner or larger wafers are very high which prohibit development at these paths; (3) 'wafering' is energy intensive process, hence expensive and carbon emission intensive. Solving these problems will enable solar electricity to reach grid parity, become affordable, and reach Terawatts scale, changing the energy landscape. Scifiniti's breakthrough technology addresses the three areas above introducing a sub \$1.00 wafer to the solar industry. Scifiniti has developed a new kerfless wafer technology that reduces the over-all LCOE by substantially reducing silicon consumption and eliminating the wafering cost. Debuted SmartWafer<sup>TM</sup>, the new technology utilizes proprietary IP. Generally labeled as Film-Silicon-on-Foreign-Substrate (FSFS) it includes deposition and crystallization of a high-purity thin Silicon (Si) absorbing layer on top of a very low cost conductive mechanicalsupport ceramic substrate. A conductive diffusion barrier layer prevents metallic contaminants from reaching the high purity silicon absorbing layer. The material chosen for this diffusion barrier enables the creation of an embedded back surface field that provides a high-quality solar cell. Adding an embedded back reflector and some optimization of the front surface texturing allows performance parity with solar cells built on mc-Si sawn wafers. Scifiniti's unique substrate is fabricated using the sintering method. It is based on low cost metallurgical grade silicon (MG-Si) and silicon carbide (SiC) ceramic composites. The material is electrically conductive to minimize the series resistance. It can also enable larger wafer form factor (8") and higher mechanical stability thereby eliminating wafer breakage. Lastly, the substrate surface can be easily structured with pyramids to allow for embedded light trapping functionality.

Keywords: smartwafer, wafer, kerf-less,

## **1 SOLUTION APPROACH**

An innovative new silicon-based wafer technology is required in order to leverage the existing polysilicon and solar cell production capacity, to rapidly expand solar manufacturing capacity, and to significantly reduce the cost of silicon solar cells and modules. SCIFINITI's *SmartWafers*<sup>TM</sup> technology produces high quality large grain silicon layers to create hybrid wafers that combine the advantages of a low-cost substrate with a "thick layer" of high quality crystalline silicon. The material stack is designed to withstand very high temperature allowing the creation of very low defect crystals with high minority carrier lifetime. The deposited silicon layer of about 30-50 microns is thin compare to standard wafers, allowing better utilization of material (less than 0.5 gram per watt compared to above 5 grams today). However, the layer is much thicker than the 1 micron "thin films" and allows for stronger absorption of the incoming photons and great efficiencies - on par and even better than standard crystalline wafer technologies. By using *SmartWafers*<sup>TM</sup>, deposition is not a rate-limiting process as in other thin film

## 2 SCIENTIFIC INNOVATION AND RELEVANCE

Scifinit's approach enable wafer cost of less than \$0.1 per watt (compared to cost of 0.25-0.35/W for c-Si wafers today) and module cost below 0.50/W. This translates to LCOE of 0.06 - 0.08/kWh. Scifinit's approach allows for thinner c-Si absorbing layer (~30µm), higher Si material utilization (only 0.4g/W), very low wafers cost, simpler and lower cost downstream cell processing (compatible with both P and N type Si), thicker supporting substrate (stronger wafers with negligible cost additions), and larger wafer form factors. It is also much different than other 'kerf-less' approaches, that are limited by: higher costs, lower material utilization, non-standard form-factors, complex wafer fabrication ("lift-off" of thin Si layers and re-attachment to handle wafers), non-standard cell process, and expensive fabrication equipment.

More than 90% of today's PV manufacturing is based on silicon wafers [1]; and due to recent improvements in manufacturing processes and the high efficiencies of the silicon-based modules that result in significant Balance of System (BOS) cost reductions, silicon's volume leadership will continue for the foreseeable future. Since the silicon wafer itself represents about half of the overall cost of a typical module [2], there are a number of research efforts to use direct-wafering, "mono-cast" silicon or to reduce the wafer thickness. While these approaches may provide incremental cost reductions, they do not offer significant cost savings and to date have resulted in only marginal or temporary cost advantages compared to established standard c-Si wafer method. In the last three years Chinese and Taiwanese solar manufacturers are leading the market in term of overall wafer production costs (W). Companies like GCL Poly, Jinko Solar, Trina and Yingli use their manufacturing cost advantages to maintain high utilization rates and set the competitive bar for other solar OEMs. According to Photon Consulting report [3], the three factors for cost advantages are silicon feedstock cost reduction, location-based cost advantages (including, labor costs, energy costs and lower materials costs), and utilization rate advantage due to better cost structure. However of these, the main advantage is still lower silicon feedstock cost. The only way for solar producers to remain competitive is through rapid cost reduction – and SCIFINITI's *SmartWafers*<sup>TM</sup> technology can deliver high cost reduction with very small capital investment.

DOE estimates that a \$1/watt installed photovoltaic energy system – equivalent to 5-6 cents/kWh – would make solar (without additional subsidies) competitive with the wholesale rate of electricity, in the U.S. [4]. According to NREL at \$1/watt, PV could generate about 14% of U.S. electricity by 2030 [5]. US DOE analysis dictates that the required component costs to reach a \$1/watt installed PV system implies the following breakdown: \$0.5/W for module costs, \$0.4/W for the BOS and installation costs, and \$0.1/W for the power electronics costs. SCIFINITI's *SmartWafers*<sup>TM</sup> technology can enable module costs of below \$0.5/W much sooner than any other technology in the market today.

SCIFINITI's SmartWafers<sup>™</sup> technology uses significantly lower amounts of high-purity silicon than current crystalline silicon wafers. SCIFINITI's SmartWafers<sup>TM</sup> technology allows the solar industry to massively expand cell manufacturing in an environmentally friendly and sustainable manner. Traditional crystalline silicon solar wafer and cell manufacturing requires large amounts of time and energy to heat silicon to temperatures above 1400°C to produce ingots, which are then sliced in a procedure that, even if executed using the industry state of the art, is still highly wasteful in terms of time, energy and material. SCIFINITI's SmartWafers™ technology saves this time, energy and material because it does not require silicon sliced from ingots. SCIFINITI's SmartWafers™ technology saves this time, energy and materials, making SmartWafers<sup>TM</sup> the most sustainable solution for making solar cell and modules.

# **3 BACKGROUND**

Until 2011 Scifiniti (formarly known as Integrated Photovoltaics Inc. or SCIFINITI) was working on the development of pure silicon deposition using proprietary ultra-clean plasma spray technique. Under this innovation SCIFINITI's starting materials were electronic grade polysilicon chunks that SCIFINITI invented ways to process into ultra clean powder that was then sprayed onto

SCIFINITI's substrates to create Si wafers. It turns out that although this was very rapid silicon deposition approach, an even more efficient way would be to skip another major step in the supply chain, the Siemens Process. In the Siemens process trichlorosilane gas (TCS) is being processed into polysilicon chunks. This step is energy intensive and the huge fabrication facilities require very large capital investments to build and to operate. Under Scifiniti's current rapid CVD approach, TCS precursor gas is being used to deposit the ultra pure Si active layer. Since 2011, SCIFINITI developed full toolset including unique, proprietary CVD tool to be able to bring an even more efficient wafer fabrication method. SCIFINITI's approach allow to skip much of today's solar Si supply chain, and it eliminates the following Si processing steps: forming highpurity polysilicon chunks using the Siemens process, converting that polysilicon into a single-crystal ingot or multi-crystal brick via melting and slow solidification, sectioning and slicing the silicon into individual wafers. Following the sectioning and slicing process, the wafers are separated, cleaned to remove cutting slurry and grit, and then etched to remove saw damage and texture the surface. SCIFINITI eliminate these steps completely. By contrast, SCIFINITI's wafers are built in three steps: a very low cost mechanical substrate made by tape casting of metallurgical grade silicon (mg-Si) and low grade silicon carbide (SiC) powders followed by high temperature ceramic sintering, deposition of barrier layer, and lastly forming a thin, high purity Si device active layer, using SCIFINITI's rapid CVD deposition method. Figure 1 shows an SEM picture of the SCIFINITI wafer structure.

Figure 1: Cross section of a SmartWafer

### 3.1 Background on Kerf-less Technology

more than 10 years ago, Professor Martin Green, a leading authority on solar technologies from the University of New South Wales (UNSW), talked about the need to move to thinner solar wafers to reduce cost and improve performance. Since then the exploding growth of solar installations and recent severe price pressure has reenforced the need to reduce the cost of the wafer by creating kerf-less processing (i.e. no sawing or cropping). The approach of thin layer micro-crystalline Si on glass or other substrates (from companies like CSG among others) had been proven to be of too low efficiency and too expensive to manufacture in large scale. Professor Green's prediction about thin wafers has become more and more obvious. There is wide agreement in the PV industry today that one of the biggest challenges is the ability to create and introduce into production the kerf-less wafers. Evaluating kerf-less wafer technologies needs to look at a multitude of criteria and cover the following attributes: a) Does the technology significantly reduce the wafer cost? b) Is the process manufactureable and scalable? c) The solar industry is high volume manufacturing – billions of wafers are being processed every year. Can the process be stable at that level? d) Is the capital equipment cost low enough? would tools cost limit the volume expansion? e) Are the wafers created by the technology compatible with current manufacturing infrastructure? In other words, are they "plug-and-play"? If not, this technology will have very limited potential as the manufacturer of these special wafers will need to develop unique cell and potentially special module technology. This will significantly increase the needed investment, limit market acceptance, and will have to compete with the over capacity that exists in the market today.

Past and current kerf-less technologies can be segmented into the following main categories

- High-Energy Implant and/or Cleaving (SiGen, TwinCreek Technologies, AstroWatt)

- Epitaxial (Epi) Growth on Porous Template and Cleaving (Solexel, Crystal Solar)

- Direct Wafering from Molten Silicon using Reusable Mold (1366)

- Ribbon Growth from Molten Silicon (Evergreen, RGS, AstroPower)

- Epitaxial growth on Seeding Substrate (Ampulse)

- Silicon Deposition on an Integrated Substrate and Recrystallization (SCIFINITI)

Although the PV industry has been looking for kerfless wafer solutions for some time, it is clear that current solutions are running into significant challenges. Although some of them work in the lab, and one of them made it to reasonable volume (String Ribbon by Evergreen Inc.), technological, production and economical (cost) issues are preventing them from achieving commercial success.

SCIFINITI engineers and management team spent a lot of time and effort in investigating and evaluating kerf-less technologies. The SCIFINITI's solution avoids the pitfalls of the companies and technologies mentioned above. The integrated substrate removes the need for a cleaving step, which eliminates manufacturability issues. Direct deposition with full layer crystallization allows fast deposition and prevents the need for the more difficult Epi growth process with a higher cost of CAPEX and OPEX. The standard wafer thickness and structure allows cell manufacturers to run a standard process in their volume manufacturing lines. The SCIFINITI approach is well thought-out, learning from previous mistakes, and can deliver the promised kerf-less value.

#### 4 RESULTS AND CONCLUSION

SCIFINITI is able to produce 6" square c-Si SmartWafers at pilot scale. SCIFINITI's technology produces crystalline silicon with efficiency equivalent to or even higher than cast multi-crystalline silicon. Industry leaders and university partners who are processing SCIFINITI's wafers to solar cells produce devices that are equal or even higher efficiency than current multi-crystalline and even mono-crystalline wafers.

By pictures, third party measurements and reports, and internal analyses SCIFINITI will demonstrate:

- (1) The material structure.

- (2) Crystalline worthy cell results of above 14.6% efficiency (Voc of about 585mV; FF of 74%; Jsc of about 33.5mA/cm<sup>2</sup>) compared with the same process results for standard crystalline wafers.

- (3) Cost analyses to support the cost-reduction claims.

- (4) Volume run results of its San Jose, CA pilot line.

## REFERENCES

- Shyam Mehta, "2009 Global PV Cell And Module Production Analysis", GTM Research, May 2010

- [2] Factory gate module costs do not include costs related to: BoS, Installation, Indirect expenses, and O&M.

- [3] "The True Cost of Power: How Low Can it Go?" Photon Consulting, July 2010

- [4] \$1/W Photovoltaic Systems, White Paper to Explore A Grand Challenge for Electricity from Solar, DOE 2010; \$1/W Workshop Summery, DOE, DOE's Website, 2010

- [5] Denholm, P., Drury, E., and Margolis, R., 2009, "The Solar Deployment System (SolarDS) Model: Documentation and Sample Results", NREL/TP-612-45832, 2009